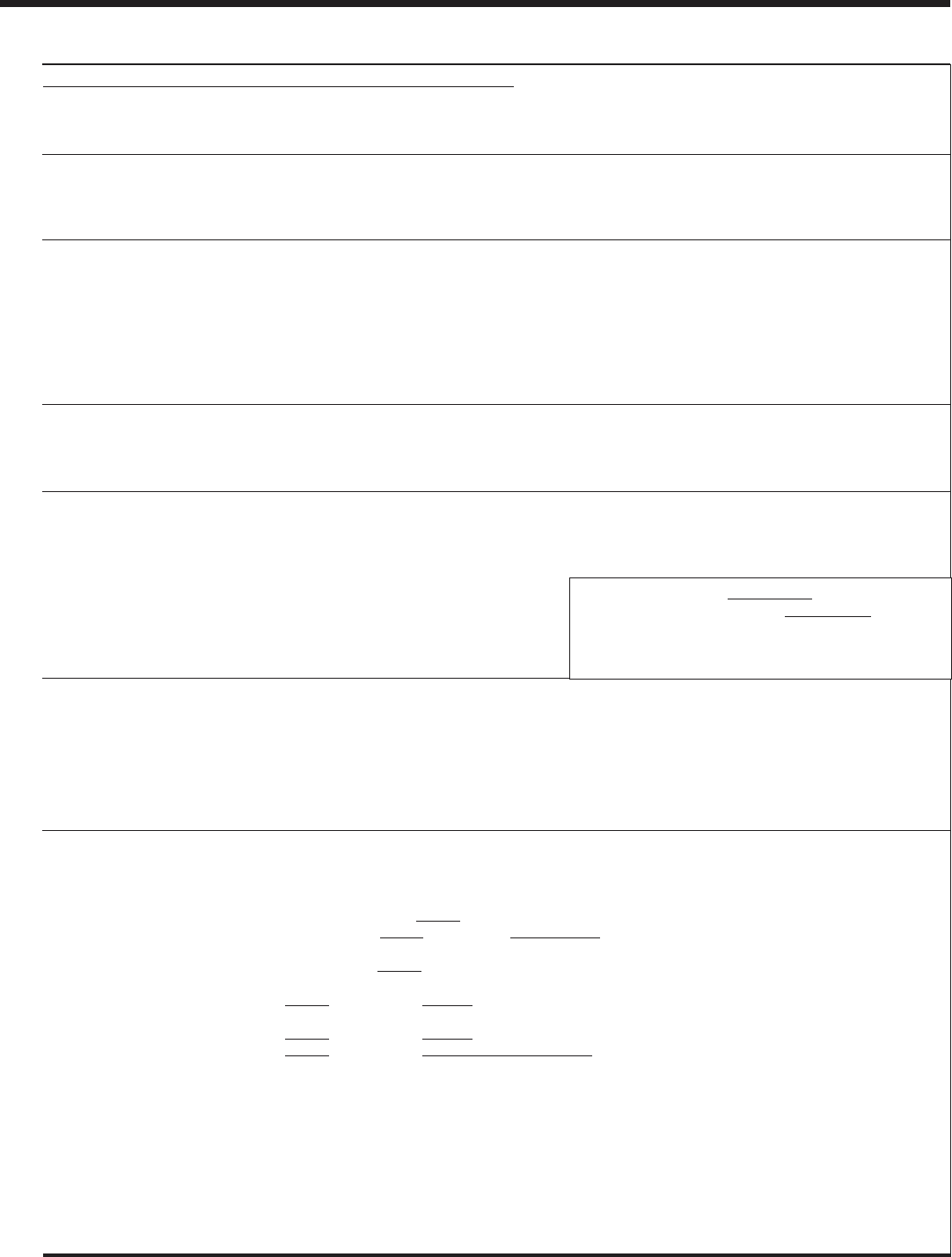

PC Processors (Pentium III - Tualatin)

Code name

Instruction architecture

MMX™ / Streaming SIMD

L1 cache - bus

L1 cache - size/controller

L1 cache - write policy

L1 cache - organization

L2 cache - size

L2 cache - data path

L2 cache - buffering

L2 cache - organization

L2 cache - controller

L2 cache - write policy

L2 cache - type

Frontside bus - speed

Memory addressability

System bus - width

System bus - parity

Execution units

Supscal dispatch/execute

Superscalar issue

Superscalar retire

Out-of-order instructions

Branch prediction

Speculative execution

Math coprocessor

Processor serial number

Serial number

Bus architecture

Internal processing

User registers

Cache line size

Power management

Multiple processors

Technology (micron)

Package type

Connector

Frequency (MHz)

Chipset support

Server blade support

All trademarks are the property of their respective owners

© IBM Corp.

(17INTEL) Compiled by Roger Dodson, IBM. January 2003

Tualatin (pronounced "TWO-ala-tin")

IA-32 / CISC/RISC/micro-ops

MMX (57 new instructions) / Streaming SIMD Extensions (70 new instructions)

64-bit / full speed

16KB data; 16KB instruction / integrated / non-blocking

Write-back or thru (data); write-thru (instruction)

4 way set associative (data); 2 way set associative (instruction)

256 or 512KB / full speed (Advanced Transfer Cache)

256-bit data path / quad-wide cache line / ECC

Intelligent buffering of read and stores (called Advanced

System Buffering with 4 writeback buffers, 6 fill buffers,

8 bus queue entries)

8-way set associative

Integrated / unified (internal die; on die)

Write-through or write-back (programmable per line), uncacheable, write-protect

Non-blocking / pipelined burst synchronous

133MHz

64GB memory addressability

64-bit system bus with ECC

ECC on system bus; parity on address bus (frontside bus)

2 integer/MMX units; 1 floating point unit; 1 load unit; 1 store unit

5 micro-ops per cycle (3 micro-ops is typical); Pipeline stages: decoupled, 14 stage superpipelined

6 micro-ops per cycle (3 micro-ops is typical)

3 micro-ops per cycle

Yes (called dynamic execution)

Dynamic (based on history) / 512 entry BTB / typically

predicts 10 to 15 nested branches

Yes (typically 20 to 30 instructions beyond counter

with an average of 5 branches)

Pipelined math coprocessor

None

Unique processor serial number

Independent backside and frontside buses operate concurrently / Dual Independent Bus Architecture (DIB)

32-bits (300 bit internal bus width)

8 GPR, 8 FP, 8 FPscalar and SIMD, 40 more GPR via register renaming

32 bytes (8 bytes x 4 chunks); burst mode bus of addr-data-data-data

System Management Mode (SMM)

Some support 2-way SMP with appropriate chipset support

0.13u

Flip-Chip Pin Grid Array-2 (FC-PGA2)

Requires Socket 370 (PGA370)

900 MHz Ultra Low Voltage (DP)

512KB L2 cache for entry-level workstations and servers (announced Jan 2003)

933 MHz Low Voltage with

512KB L2 cache for blade servers (announced September 2002)

1.0A GHz 256KB L2 cache for desktop, entry-level workstations and servers (announced August 2001)

1.0 GHz Low Voltage (DP) 512KB L2 cache for entry-level workstations and servers (announced January 2003)

1.13A GHz 256KB L2 cache for desktop, entry-level workstations and servers (announced August 2001)

1.13 GHz-S

512KB L2 cache for servers (announced June 2001)

1.20 GHz 256KB L2 cache for desktop, entry-level workstations and servers (announce August 2001)

1.26 GHz-S

512KB L2 cache for servers (announced August 2001)

1.4 GHz-S

512KB L2 cache for servers and blade servers (announced January 2002)

Intel 815x, 820x, 840 and others

ServerWorks

®

HE-SL and others

Pentium III at 933MHz and 1.4GHz supported in "Performance Server Blades"

Intel

®

Pentium

®

III for desktop and entry-level workstations and servers

L2 cache bus also called Backside Bus

Memory or system bus also called

Frontside Bus

Created by IBM PC Institute

Personal Systems Reference (PSREF)