CC2420

SWRS041B Page 81 of 89

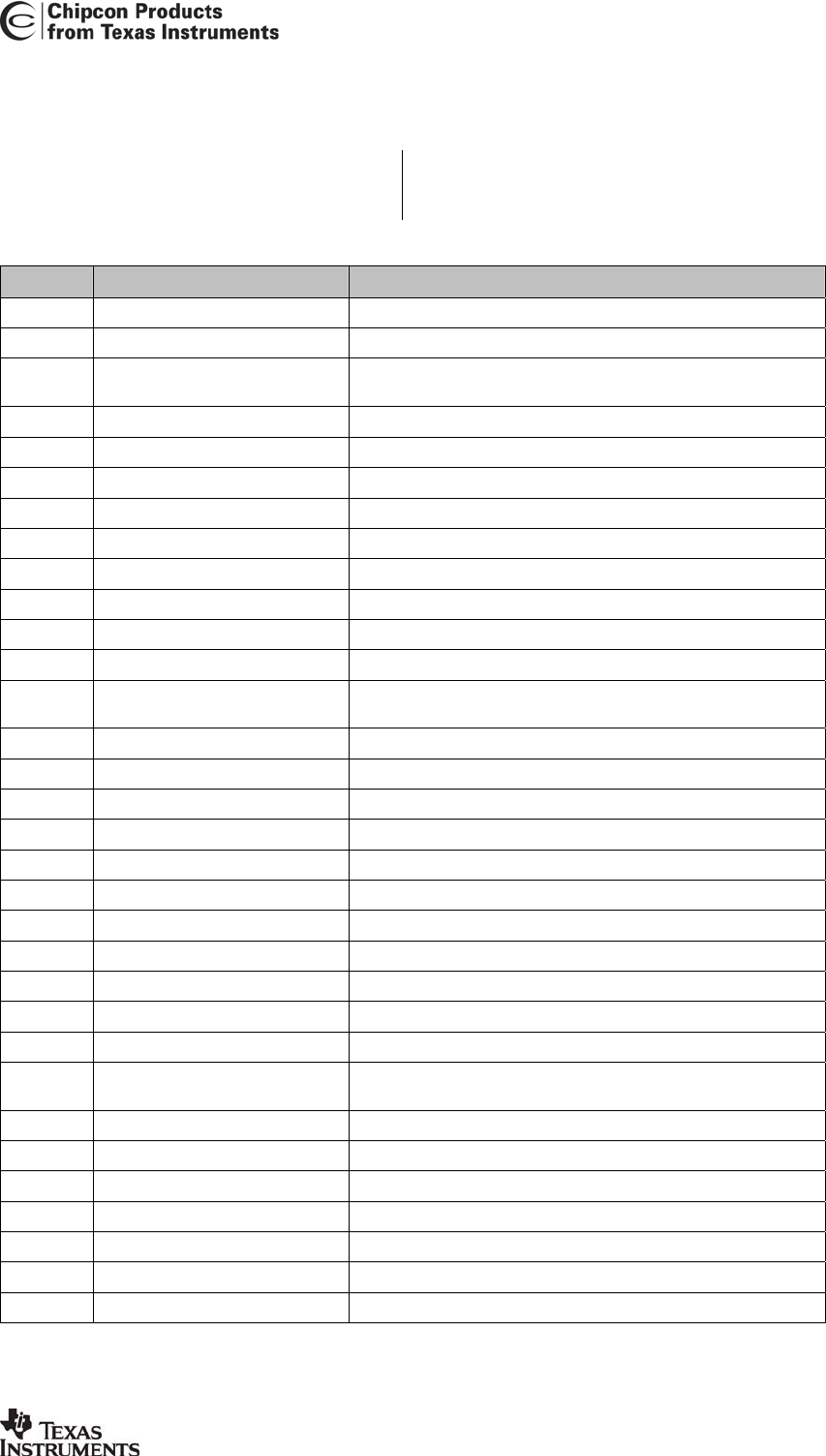

38 Test Output Signals

The two digital output pins CCA and SFD,

can be set up to output test signals

defined by IOCFG1.CCAMUX and

IOCFG1.SFDMUX. This is summarized in

Table 12 and Table 13 below.

CCAMUX

Signal output on CCA pin Description

0 CCA Normal operation

1 ADC_Q[0] ADC, Q-branch, LSB used for random number generation

2 DEMOD_RESYNC_LATE High one 16 MHz clock cycle each time the demodulator

resynchronises late

3 LOCK_STATUS Lock status, same as FSCTRL.LOCK_STATUS

4 MOD_CHIPCLK Chip rate clock signal during transmission

5 MOD_SERIAL_CLK Bit rate clock signal during transmission

6 FFCTRL_FS_PD Frequency synthesizer power down, active high

7 FFCTRL_ADC_PD ADC power down, active high

8 FFCTRL_VGA_PD VGA power down, active high

9 FFCTRL_RXBPF_PD Receiver bandpass filter power down, active high

10 FFCTRL_LNAMIX_PD Receiver LNA / Mixer power down, active high

11 FFCTRL_PA_P_PD Power amplifier power down, active high

12 AGC_UPDATE High one 16 MHz clock cycle each time the AGC updates its gain

setting

13 VGA_PEAK_DET[1] VGA Peak detector, gain stage 1

14 VGA_PEAK_DET[3] VGA Peak detector, gain stage 3

15 AGC_LNAMIX_GAINMODE[1] RF receiver front-end gain mode, bit 1

16 AGC_VGA_GAIN[1] VGA gain setting, bit 1

17 VGA_RESET_N VGA peak-detector reset sign, active low.

18 - Reserved

19 - Reserved

20 - Reserved

21 - Reserved

22 - Reserved

23 CLK_8M 8 MHz clock signal output

24 XOSC16M_STABLE 16 MHz crystal oscillator stabilised, same as the status bit in Table

5

25 FSDIG_FREF Frequency synthesizer, 4 MHz reference signal

26 FSDIG_FPLL Frequency synthesizer, 4 MHz divided signal

27 FSDIG_LOCK_WINDOW Frequency synthesizer, lock window

28 WINDOW_SYNC Frequency synthesizer, synchronized lock window

29 CLK_ADC ADC clock signal 1

30 ZERO Low

31 ONE High

Table 12. CCA test signal select table