4-5

Chapter 4: BIOS

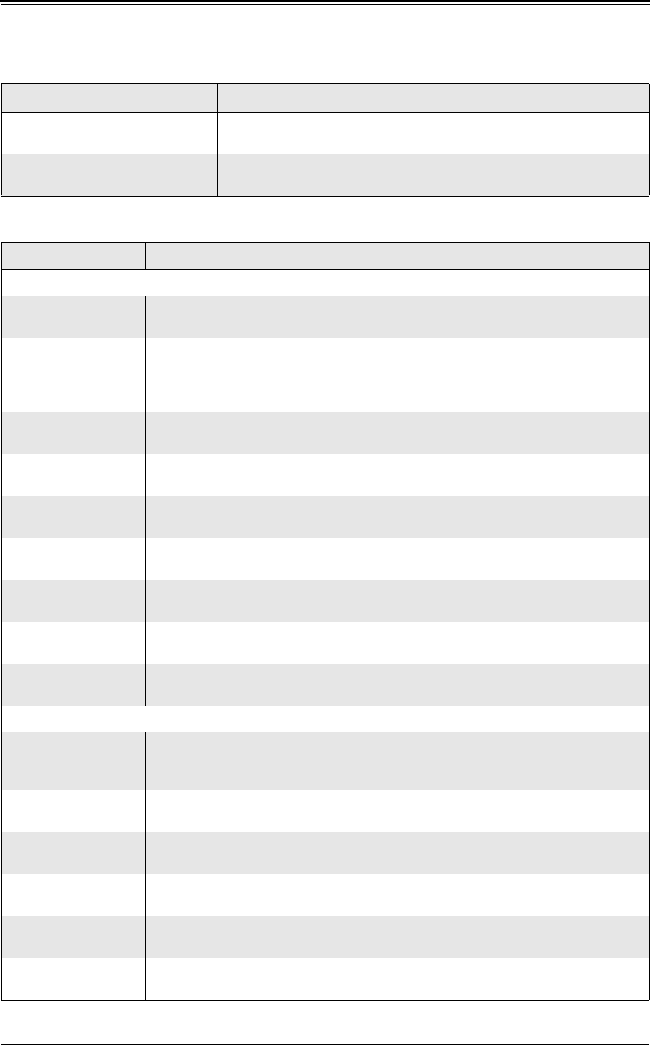

Table 4-4. Advanced Chipset Control Submenu

Menu Item Description

NorthBridge Configuration

submenu

See Table 4-5 for further details and submenus.

SouthBridge Configuration

submenu

See Table 4-6 for further details and submenus.

Table 4-5. NorthBridge Configuration Submenu

Menu Item Description

Memory Configuration

Bank Interleaving

Select Auto to automatically enable a bank-interleaving memory scheme when

this function is supported by the processor. The options are Auto and D

ISABLED.

Channel

Interleaving

Selects the channel-interleaving memory scheme when this function is

supported by the processor. The options are D

ISABLED, ADDRESS BITS 6,

A

DDRESS BITS 12, XOR of Address Bits [20:16, 6] and XOR OF ADDRESS BITS

[20:16, 9].

Enable Clock to

All Dimms

Use this setting to enable unused clocks to all DIMMSs, even if some DIMM slots

are unpopulated. Options are E

NABLED and Disabled.

Mem Clk Tristate

C3/ALTVID

Use this setting to E

NABLE or Disable memory clock tristate during C3 and ALT

VID.

Memory Hole

Remapping

When Enabled, this feature enables hardware memory remapping around the

memory hole. Options are Enabled and D

ISABLED.

CS Sparing

This setting will reserve a spare memory rank in each node when enabled.

Options are E

NABLE and Disable.

DCT Unganged

Mode

This setting enables unganged DRAM mode (64-bit). Options are AUTO (ganged

mode) and Always (unganged mode).

Power Down

Enable

This setting enables or disables the DDR power down mode. Options are

Enabled and D

ISABLED.

Power Down

Mode

This sets the power down mode. Options are Channel and CHIP SELECT.

ECC Configuration

ECC Mode

This setting affects the DRAM scrub rate based on its setting. Options are

D

ISABLED, Basic, GOOD, SUPER, MAX and USER. Depending upon the setting

chosen, some or all of the following settings will become active:

DRAM ECC

Enable

DRAM ECC allows hardware to report and correct memory errors automatically.

Options are Enabled and D

ISABLED.

DRAM SCRUB

REDIRECT

Allows system to correct DRAM ECC errors immediately, even with background

scrubbing on. Options are Enabled and D

ISABLED.

4-Bit ECC

Mode

Allows the user to enabled 4-bit ECC mode (also known as ECC Chipkill).

Options are E

NABLED and Disabled.

DRAM BG

Scrub

Corrects memory errors so later reads are correct. Options are Disabled and

various times in nanoseconds and microseconds.

Data Cache BG

Scrub

Allows L1 cache RAM to be corrected when idle. Options are Disabled and

various times in nanoseconds and microseconds.