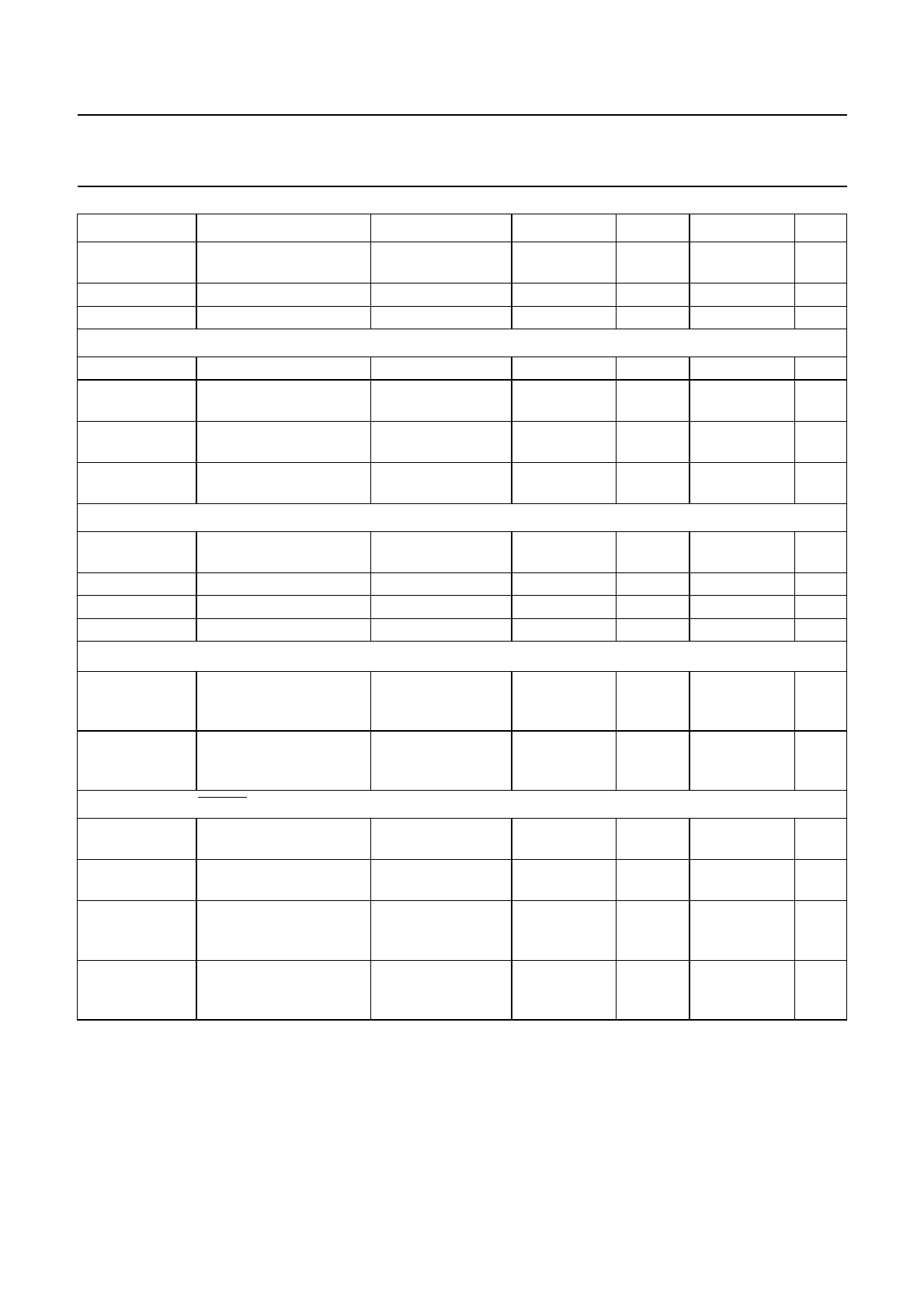

2004 Jan 26 63

Philips Semiconductors Product specification

MPEG-2 video and MPEG-audio/AC-3

audio encoder with multiplexer

SAA6752HS

V

IH

HIGH-level input voltage if used with external

clock

1.7 − V

DDA

V

C

shunt

shunt capacitance −−7pF

R

s

serial resistance −−25 Ω

Crystal oscillator tuning: pins XTALI and XTALO; note 10

N

tune

tuning steps −127 − +128

C

tune(min)

minimum internal tuning

capacitance to V

SSA

N

tune

= 128 − 8 − pF

C

tune(max)

maximum internal tuning

capacitance

N

tune

= −127 − 72 − pF

f

step

crystal frequency offset

per tuning step

14 42 70 Hz

External clock input: pin EXTCLK

f

EXTCLK

external frequency square wave;

note 11

25.7 27.0 28.3 MHz

δ duty factor t

HIGH

/T

cy

40 50 60 %

t

r(EXTCLK)

rise time V

I

= 0.7 to 1.7 V −−5ns

t

f(EXTCLK)

fall time V

I

= 1.7 to 0.7 V −−6ns

I

2

C-bus address select input: pin I2CADDRSEL

V

IL

LOW-level input voltage

for I

2

C-bus addresses

40H and 41H

−0.5 − +0.7 V

V

IH

HIGH-level input voltage

for I

2

C-bus addresses

42H and 43H

1.7 − V

DDP

V

Reset input: pin RESET

V

IL

LOW-level input voltage

for active reset

−0.5 − +0.7 V

t

start

start time of first reset

pulse after power-on

− 010 µs

t

length

length of reset pulse

after power-on and after

sleep

10 −− ms

t

init

initialization phase after

reset pulse until I

2

C-bus

commands are accepted

−−1s

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT