2004 Jan 26 64

Philips Semiconductors Product specification

MPEG-2 video and MPEG-audio/AC-3

audio encoder with multiplexer

SAA6752HS

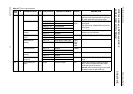

SDRAM interface data, address and control timing: pins SD_DQ31 to SD_DQ0, SD_A13 to SD_A0, SD_CAS,

SD_RAS, SD_WE and SD_OE

T

cy

cycle time f

sys

= 27 MHz − 9.26 − ns

t

CAS

CAS latency time − 3 − clock

cycles

t

RCD

row to column delay time − 3T

cy

− ns

t

RRD

activate to activate delay

time

− 2T

cy

− ns

t

RP

row precharge time − 3T

cy

− ns

t

WR

write recovery time − 2T

cy

− ns

t

RSC

mode register set cycle

time

− 2T

cy

− ns

t

RAS

row activate time − 6T

cy

− ns

t

RC

row cycle time − 8T

cy

− ns

t

power-up

wait time after power-on 500 515 −µs

t

d(C-D)

clock to data output

delay

C

L(SD_CLK)

= 15 pF;

C

L(SD_DQn)

= 8 pF;

f

SD_CLK

= 108 MHz

2.5 4.0 5.0 ns

t

d(C-A)

clock to address output

delay

C

L(SD_CLK)

= 15 pF;

C

L(SD_An)

= 8 pF;

f

SD_CLK

= 108 MHz

2.5 4.0 5.0 ns

t

su(D)

data input set-up time 1 −− ns

t

h(D)

data input hold time 2.5 −− ns

Data output interface timing: pins PDO7 to PDO0, PDIDS, PDOSYNC, PDOAV and PDIOCLK

t

l-o(PDIDS-PDOVAL)

PDIDS to PDOVAL

low-ohmic time

DEBI slave mode 0 − 20 ns

t

l-o(PDIDS-PDO)

PDIDS to PDO[7:0]

low-ohmic time

DEBI slave mode 0 − 20 ns

t

stab(PDO-PDOVAL)

PDO[7:0] data stable to

falling PDOVAL time

DEBI slave mode 10 −− ns

t

r(PDOVAL-PDO)

rising

PDOVAL to PDO[7:0]

high-impedance time

DEBI slave mode 10 −− ns

t

h(PDO-PDIOCLK)

PDO[7:0] data to

PDIOCLK hold time

DIO master mode;

PDOVAL = 1

10 −− ns

t

su(PDO-PDIOCLK)

PDO[7:0] data to

PDIOCLK set-up time

DIO master mode;

PDOVAL = 1

10 −− ns

t

i(PDIOCLK)H

input PDIOCLK HIGH

time

DIO slave mode 55 −− ns

t

i(PDIOCLK)L

input PDIOCLK LOW

time

DIO slave mode 55 −− ns

t

stab(PDIOCLK-PDO)

falling input PDIOCLK to

PDO[7:0] data stable

time

DIO slave mode;

PDOVAL = 1

36 − 58 ns

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT