2004 Jan 26 65

Philips Semiconductors Product specification

MPEG-2 video and MPEG-audio/AC-3

audio encoder with multiplexer

SAA6752HS

Notes

1. Short-circuit current is only allowed for a short time (<1 s).

2. The output pins are 3.3 V tolerant when in 3-state mode.

3. Pins SCL and SDA of the I

2

C-bus interface do not obstruct the SDA and SCL lines if the supply voltage V

DDP

is

switched off.

4. The open-drain outputs are 3.3 V tolerant.

5. Frame-locked input data rate deviation from SAA6752HS crystal clock.

6. Supporting output range of the Philips SAA7114 video input processor.

7. Applies for line frequencies ±2% from nominal.

8. Minimum limit according to IEC 60756; maximum limit because the SAA6752HS may drop frames for V-sync

frequencies greater than 1.5% above nominal.

9. Deviation according to IEC 60756.7. The SAA6752HS will only encode 240 lines (when in 525-line mode) and

288 lines (when in 625-line mode). Therefore any additional lines in a field above these values will not be encoded.

10. Pin XTALO has to be used for connection with a crystal only. Do not use for other purposes.

11. The required stability of the crystal frequency or external system clock is dependent upon the clock mode used in the

application.

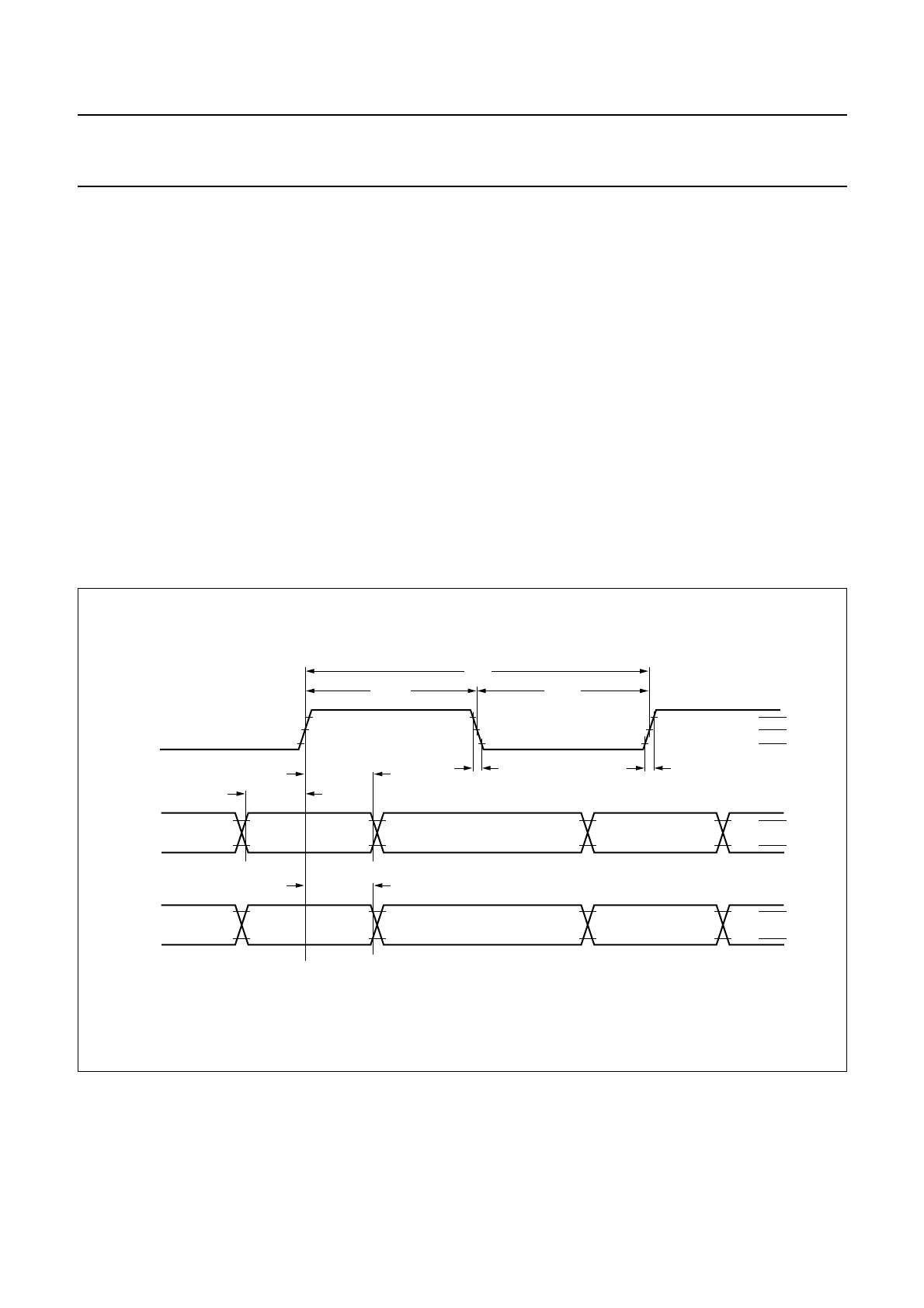

handbook, full pagewidth

MHC142

valid not valid valid

1.7 V

0.7 V

1.7 V

1.3 V

0.7 V

data and

control

inputs

VCLK

T

cy

t

LOW

t

HIGH

valid not valid valid

2.4 V

0.4 V

data and

control

outputs

t

f(VCLK)

t

HD;DAT

t

r(VCLK)

t

SU;DAT

t

OH;DAT

Fig.15 Clock data timing.