29

3.6) IMUXP0 – Local Mux Interrupt Control Register (offset 10, read/write)

This register is used to set individual interrupts for each optically isolated input.

Effectively MUXP0 is used as address lines to map each optically isolated inputs to a

specific IRQ. If any one of the Opto-isolators was enabled, the pulse is set up and

vectored to the Decoder to a specific IRQ. This register configures this line to any of 8

IRQs lines.

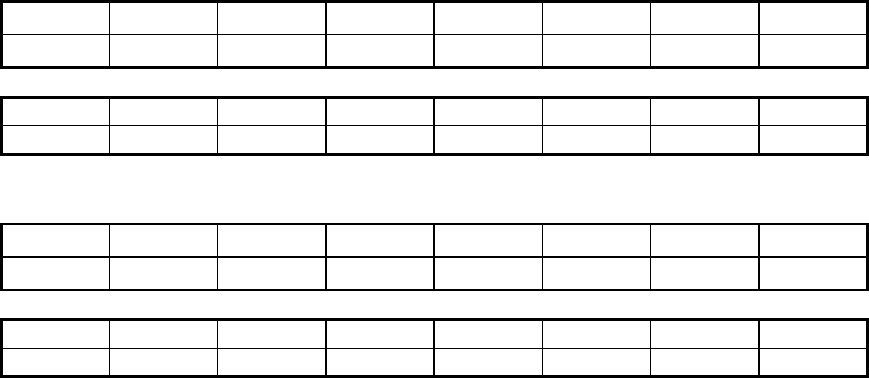

IMUXP0 Register (write mode)

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

MUXP5A0

MUXP4A2

MUXP4A1

MUXP4A0

MUXP3A2

MUXP3A1

MUXP3A0

MUXP2A2

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

MUXP2A1 MUXP2A0

MUXP1A2 MUXP1A1

MUXP1A0 MUXP0A2 MUXP0A1

MUXP0A0

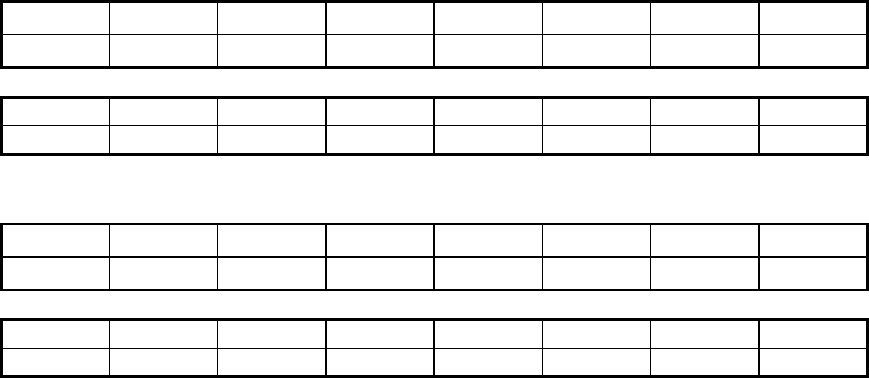

IMUXP0 Register (read mode)

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

MUXP5A0

MUXP4A2

MUXP4A1

MUXP4A0

MUXP3A2

MUXP3A1

MUXP3A0

MUXP2A2

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

MUXP2A1 MUXP2A0

MUXP1A2 MUXP1A1

MUXP1A0 MUXP0A2 MUXP0A1

MUXP0A0

Bits 0-2: MUXP0A0 to MUXP0A2 - These bits are used to set up an IRQ line for the

Opto-isolator 0 (PA0). Bits 0 to 2 sets the IRQ selection for Opto-Isolator 0, with

IGATE0 enabling/disable interrupt support. IGATE0 must be enabled in order to

select an interrupt. Table 3.6a determines the appropriate writes to Bits 0 to 2 to

select 1 of 8 IRQs.

Reading these bits determines the status of MUXP0A0 to MUXP0A2.