Functional Architecture Intel® Server Board SE7501WV2

Revision 1.0

Intel reference number C25653-001

22

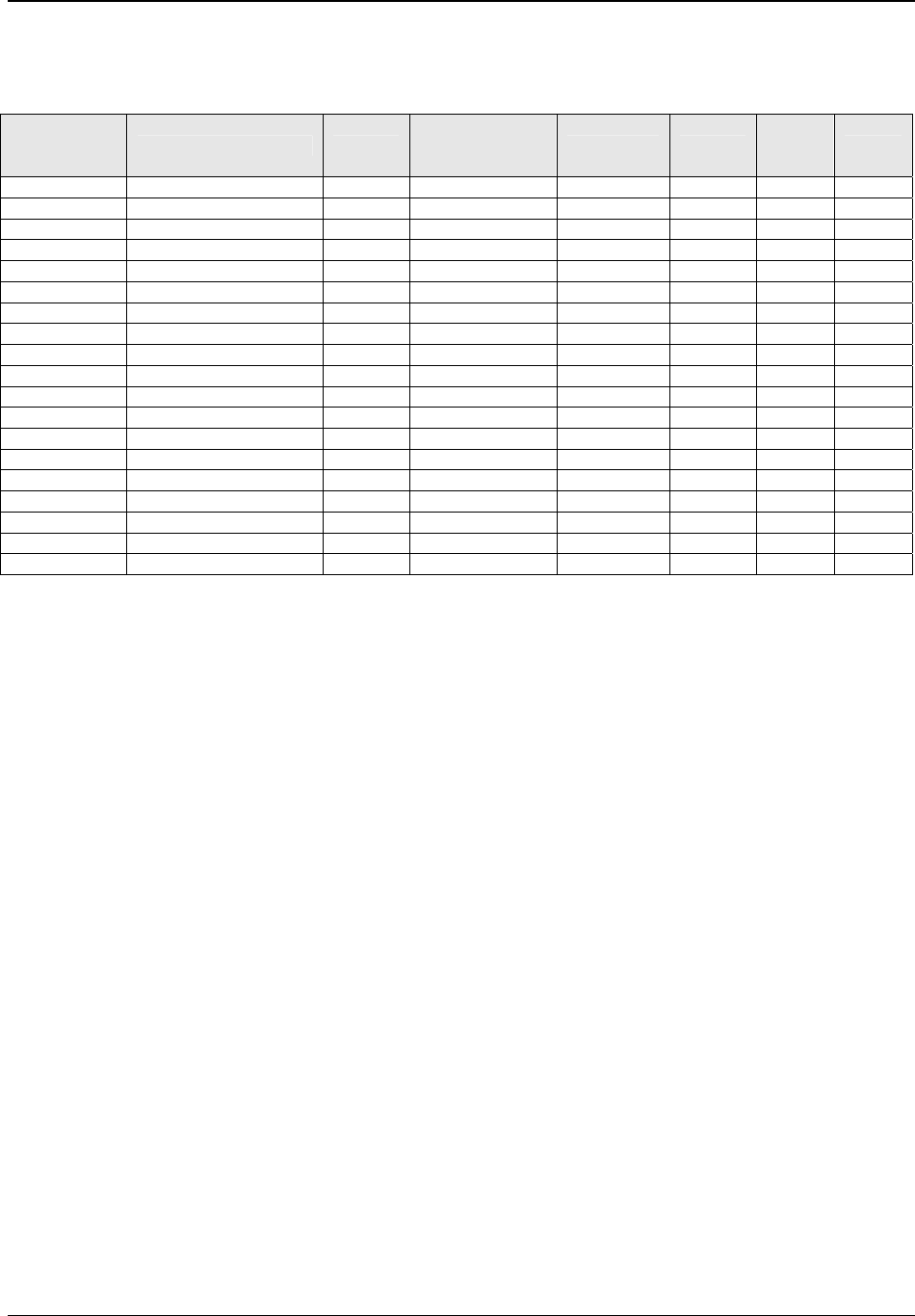

Table 2. Intel

®

Server Board SE7501WV2 Processor Support Matrix for 400MHz

Speed (MHz)

400MHz

Product Code MM#

Test

Specification

(S-spec)

Stepping CPUID

L2

Cache

Size

Notes

2.8 GHz BX80532KC2800D 850007 SL6MS C1 0F24 512k 1

2.8 GHz 80532KC072512 849546 SL6M7 C1 0F24 512k 1

2.8GHz (1U) BX80532KC2800DU 850614 SL6M7 C1 0F24 512k 1

2.6 GHz BX80532KC2600D 850609 SL6EQ C1 0F24 512k 1

2.6 GHz 80532KC064512 847694 SL6EQ C1 0F24 512k 1

2.6 GHz (1U) BX80532KC2600DU 849701 SL6EQ C1 0F24 512k 1

2.4 GHz BX80532KC2400D 845163 SL687 tB0 0F24 512k 1

2.4 GHz 80532KC056512 847695 SL6EP C1 0F24 512k 1

2.4 GHz BX80532KC2400D 851738 SL6EP C1 0F24 512k 1

2.4 GHz (1U) BX80532KC2400DU 849703 SL6K2 B0 0F24 512k 1

2.2 GHz BX80532KC2200D 843623 SL624 tB0 0F24 512k 1

2.2 GHz 80532KC049512 849112 SL6JZ C1 0F24 512k 1

2.2 GHz BX80532KC2200D 49356 SL6JZ C1 0F24 512k 1

2.2 GHz (1U) BX80532KC2200DU 848431 SL624 tB0 0F24 512k 1

2.0 GHz BX80532KC2000D 843637 SL623 tB0 0F24 512k 1

2.0 GHz 80532KC041512 849063 SL6JY C1 0F24 512k 1

1.8 GHz BX80532KC1800D 843620 SL622 tB0 0F24 512k 1

1.8 GHz 80532KC033512 849064 SL6JX C1 0F24 512k 1

1.8 GHz (1U) BX80532KC1800DU 848419 SL622 tB0 0F24 512k 1

Notes: Processors must be populated in sequential order. That is, CPU socket #1 must be

populated before CPU socket #2.

• The SE7501WV2 server board is designed to provide up to 75 A per processor.

Processors with higher current requirements are not supported.

• Processor terminators are not required in unpopulated processor sockets.

In addition to the circuitry described above, the processor subsystem contains the following:

• Processor module presence detection logic

• Server management registers and sensors

3.1.1.1 Processor VRM

The SE7501WV2 baseboard has a single VRM (Voltage Regulator Module) to support two

processors. It is compliant with the VRM 9.1 specification and provides a maximum of 150

AMPs, which is capable of supporting currenlyt supported processors as well as those

supported in the future.

The board hardware and BMC must read the processor VID (voltage identification) bits for each

processor before turning on the VRM. If the VIDs of the two processors are not identical, then

the BMC will not turn on the VRM and a beep code is generated.