Intel® Server Board SE7501WV2 TPS Server Management

Revision 1.0

Intel reference number C25653-001

63

5.2.3 Soft Reset

A soft reset causes the processors to begin execution in a known state without flushing caches

or internal buffers. Soft resets can be generated by the keyboard controller located in the SIO,

by the ICH3-S, or by the operating system.

5.3 Intelligent Platform Management Buses (IPMB)

Management controllers (and sensors) communicate on the I

2

C-based Intelligent Platform

Management Bus. A bit protocol, defined by the I

2

C Bus Specification, and a byte-level protocol,

defined by the Intelligent Platform Management Bus Communications Protocol Specification,

provide an independent interconnect for all devices operating on this I

2

C bus.

The IPMB extends throughout the server board and system chassis. An added layer in the

protocol supports transactions between multiple servers on Inter-Chassis Management Bus

(ICMB) I

2

C segments.

The server board provides a 3-pin IPMB connector to support add-in cards with IPMB interface.

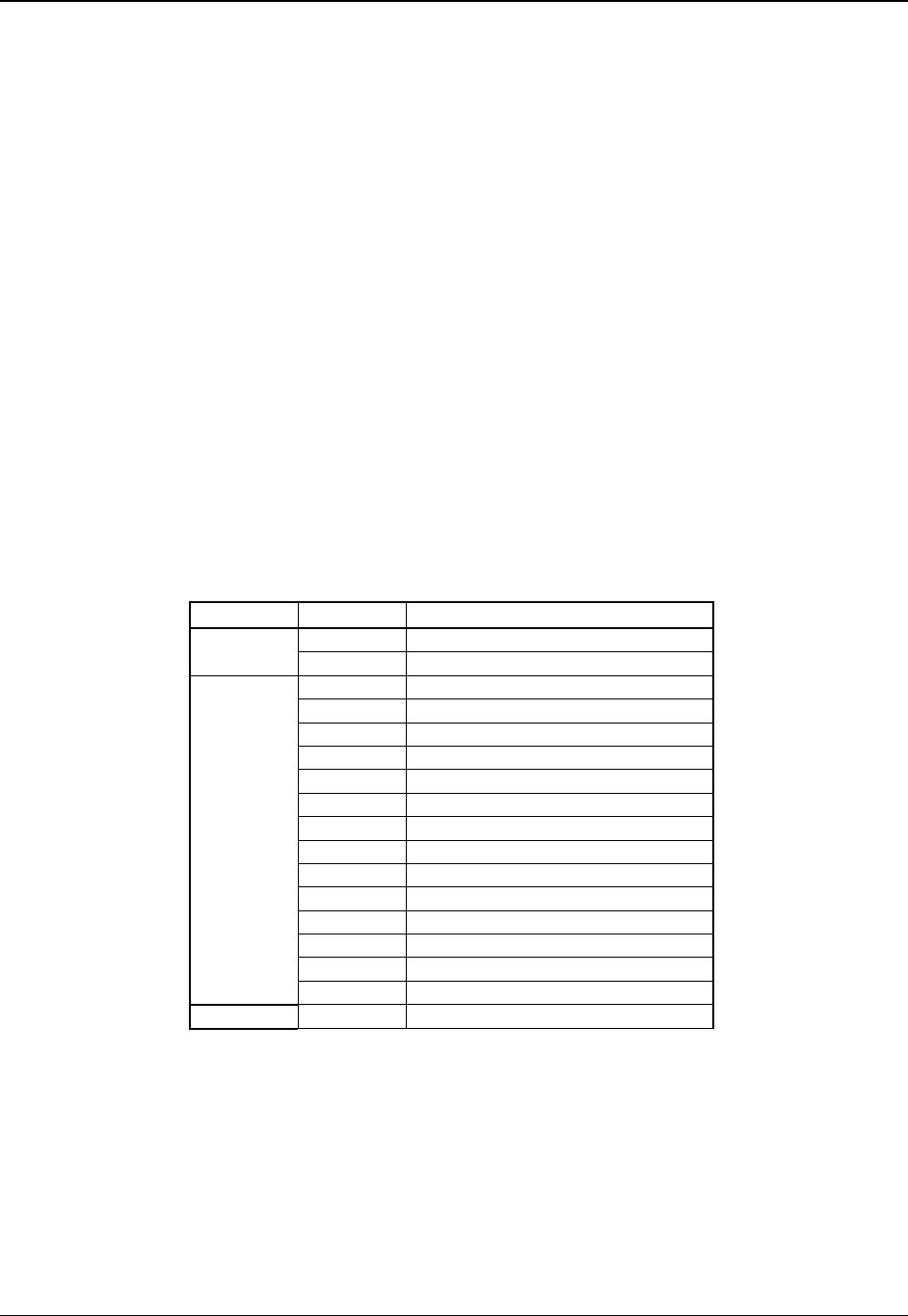

In addition to the “public” IPMB, the BMC also has three private I

2

C busses. The BMC is the

only master on the private busses. The following table lists all server board connections to the

Sahalee BMC private I

2

C busses.

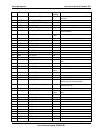

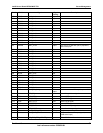

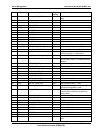

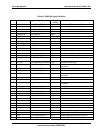

Table 23. Intel

®

Server Board SE7501WV2 I2C Address Map

I

2

C Bus I2C Addr Device

0x58 Heceta5 PB1

0x60 SIO

0x30 CPU1 therm sensor

0x32 CPU2 therm sensor

0x44 ICH3

0x60 MCH

0xA0 DIMM1

0xA2 DIMM3

0xA4 DIMM5

0xA6 CPU1 SEEPROM

0xA8 DIMM2

0xAA DIMM4

0xAC DIMM6

0xAE CPU2 SEEPROM

0xC4 P64H2

PB3

0xD2 CK408B

PB4 NIC

5.4 Inter Chassis Management Bus (ICMB)

The BMC on the SE7501WV2 server board has built in support for ICMB interface. An optional

ICMB card is required to use this feature because the ICMB transceivers are not provided on

the server board. A 5-pin ICMB connector on the SE7501WV2 board provides the interface to

the ICMB module.