Configuration and Initialization Intel® Server Board SE7501WV2 TPS

Revision 1.0

Intel reference number C25653-001

44

4.6 PCI I/O Subsystem

4.6.1 PCI Subsystem

The primary I/O bus for the SE7501WV2 server board is the PCI subsystem, with three

independent PCI bus segments. The PCI bus complies with the PCI Local Bus Specification,

Rev 2.2. The P32-A bus segment is directed through the ICH South Bridge while the two 64-bit

segments, P64-B and P64-C, are directed through the P64H2 I/O Bridge. The following table

lists the characteristics of the three PCI bus segments.

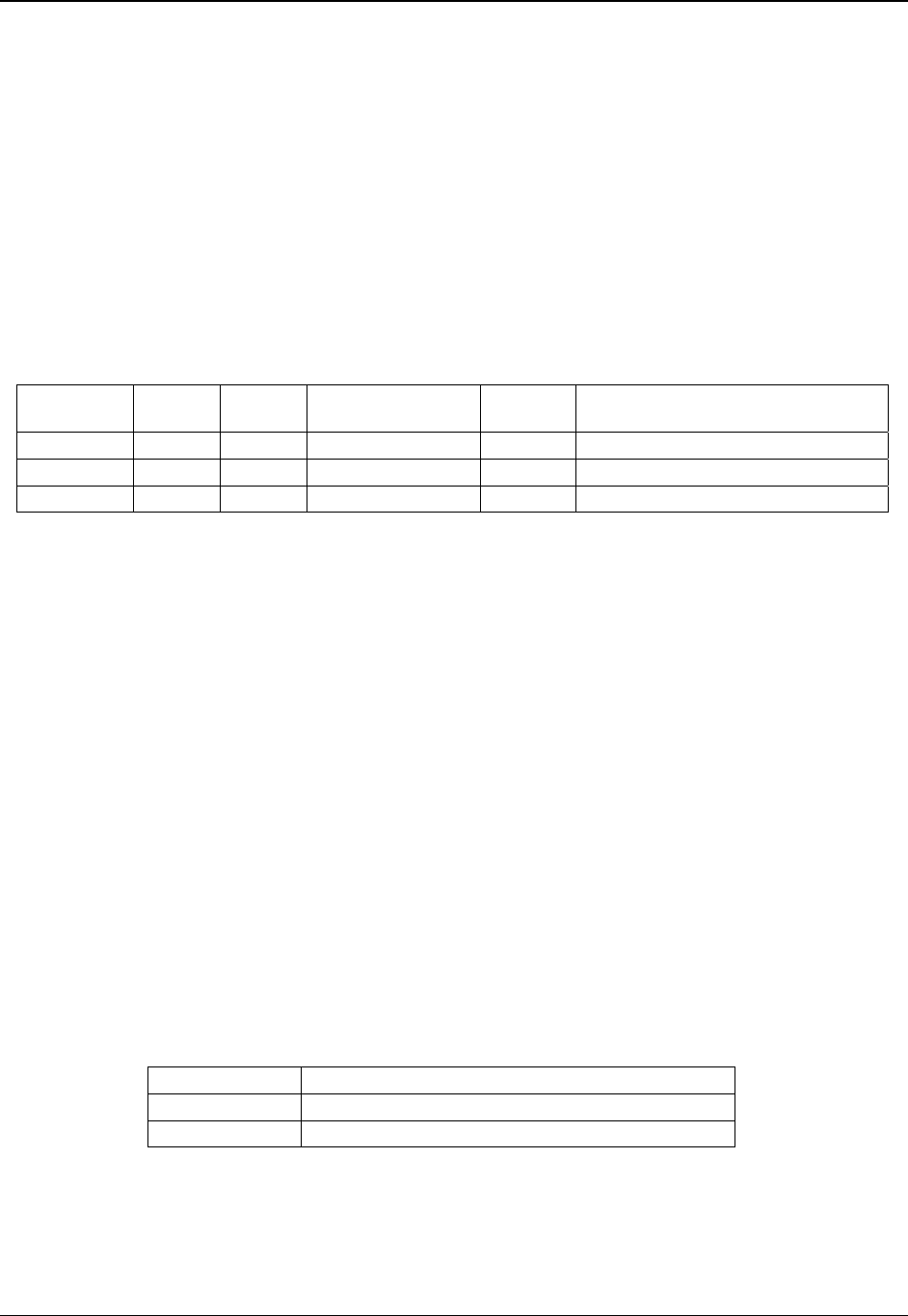

Table 10. PCI Bus Segment Characteristics

PCI Bus

Segment

Voltage Width Speed Type PCI I/O Riser Slots

P32-A 5 V 32-bits PCI 33 MHz Peer Bus –

P64-B 3 V 64-bits PCI-X 100 MHz Peer Bus Supports full-length cards, 3.3V bus

P64-C 3 V 64-bits PCI-X 100 MHz Peer Bus Supports low-profile cards, 3.3V bus

4.6.2 P32-A: 32-bit, 33-MHz PCI Subsystem

All 32-bit, 33-MHz PCI I/O for the SE7501WV2 server board is directed through the ICH South

Bridge. The 32-bit, 33-MHz PCI segment created by the ICH is known as the P32-A segment.

The P32-A segment supports the following embedded devices and connectors:

• 2D/3D Graphics Accelerator: ATI Rage* XL Video Controller

• ATA-100 controller: Promise Technology* PDC20277

Each of the embedded devices listed above can be disabled via a BIOS Setup option.

4.6.2.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD[31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a

unique PCI device ID value for use in configuration cycles. The following table shows the bit to

which each IDSEL signal is attached for P32-A devices and the corresponding device description.

Table 11. P32-A Configuration IDs

IDSEL Value Device

28 ATI Rage XL Video Controller

18 ATA-100 controller Promise Technology PDC20277

4.6.2.2 P32-A Arbitration

P32-A supports three PCI masters (ATA Rage XL, Promise ATA-100 Controller, and the ICH3-

S). All PCI masters must arbitrate for PCI access, using resources supplied by the ICH. The