Server Management Intel® Server Board SE7501WV2 TPS

Revision 1.0

Intel reference number C25653-001

58

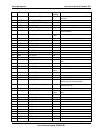

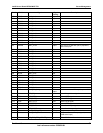

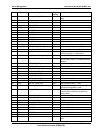

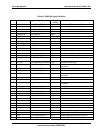

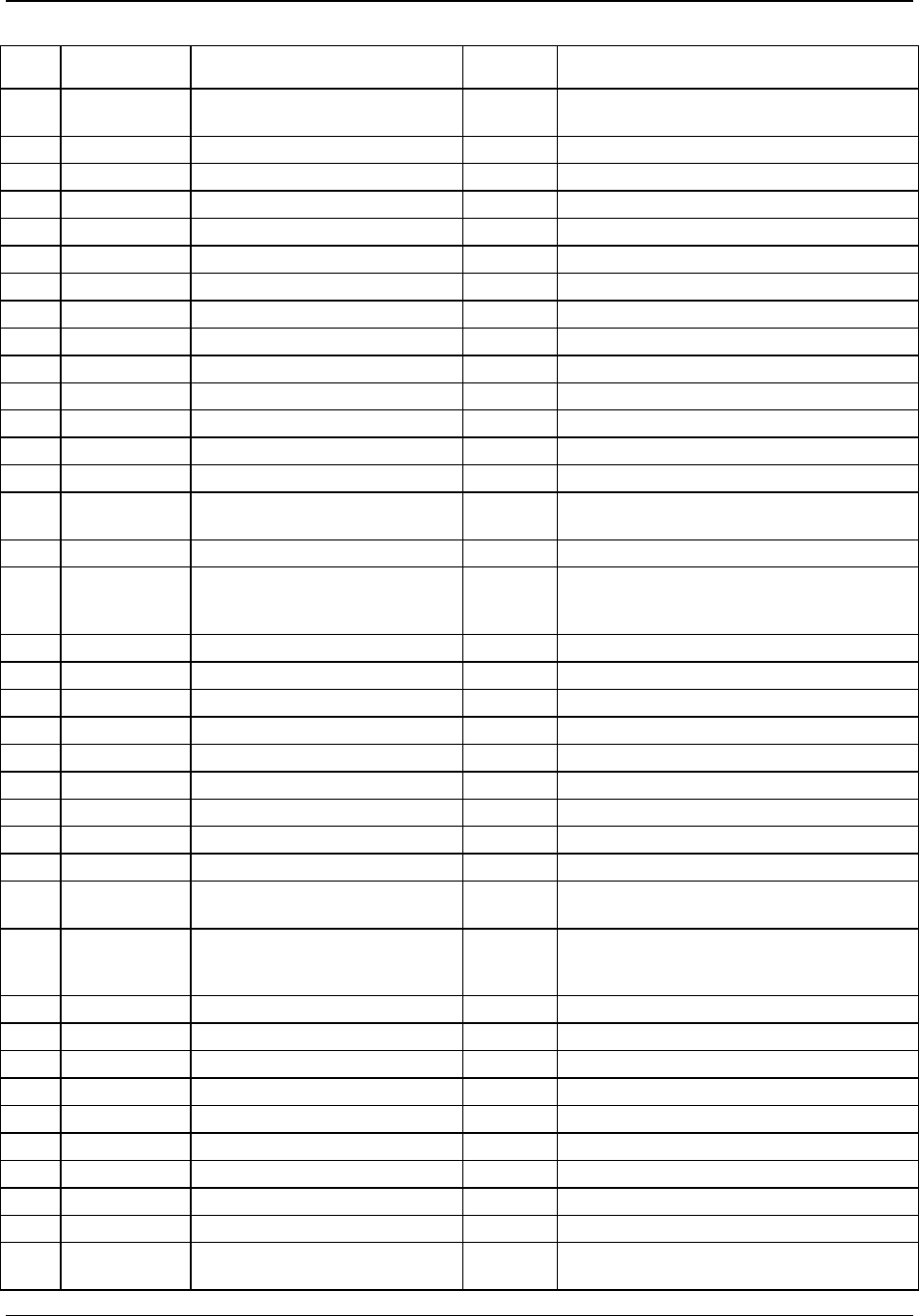

Pin # Pin Name Signal Type/

Config

Description

H12 RTS1* BMC_ICMB_TX_ENB _L TP output ICMB transceiver enable signal, asserted by

BMC

G14 RX1 BMC_ICMB_RX input ICMB serial receive data

G13 TX1 BMC_ICMB_TX output ICMB serial send data

A12 TIC1_OUT BMC_SPKR_L TP output BMC speaker tone enable signal (for beeps)

B12 TIC2_IN0 FAN_TACH1 input

A13 TIC2_IN1 FAN_TACH2 input

B13 TIC2_IN2 FAN_TACH3 input

B14 TIC2_IN3 FAN_TACH4 input

C13 TIC2_IN4 FAN_TACH5 input

C14 TIC2_IN5 FAN_TACH6 input PWT fan, CPU1

D13 TIC2_IN6 FAN_TACH7 input PWT fan, CPU2

D12 TIC2_IN7 BMC_CPU1_SKTOCC_L input Socket occupied signal from CPU1

D14 TIC3_0UT BMC_CPU2_SKTOCC_L input Socket occupied signal from CPU2

E11 TIC4_IN SIO_CLK_32K_RTC_BMC input 32kHz clock signal from IHC3

C10 LED0 BSEL_EQUAL_L input XOR gate compares CPU’s BSEL: if equal,

XOR will output a LO. Otherwise HI

A10 LED1 ZZ_BMC_ROLLING_BIOS_L TP output ROLLING BIOS flash control pin

B10 LED2 ZZ_SPA_SWITCH_EN TP output Connects to serial port Mux logic allowing

SPA to route to back in 1U chassis with SOL

enabled

D11 LED3 BMC_PWR_BTN_L TP output Power button signal from BMC to ICH3

A11 LED4 BMC_PS_PWR_ON_L TP output Power On signal to power supply

C11 LED5 RST_P6_PWR_GOOD TP output Chipset power good/rst signal

A6 SDA0 IPMB_I2C_5VSB_SDA bidir IPMB I2C data

B6 SCL0 IPMB_I2C_5VSB_SCL bidir IPMB I2C clock

B7 SDA1 SMB_I2C_3VSB_SDA bidir SMB I2C Bus data

D7 SCL1 SMB_I2C_3VSB_SCL bidir SMB I2C Bus clock

C8 SDA2 PB1_I2C_5VSB_SDA bidir BMC Private I2C Bus 1 - data.

A7 SCL2 PB1_I2C_5VSB_SCL bidir BMC Private I2C Bus 1 - clock.

B8 SDA3 SERIAL_TO_LAN_L TP output Serial bus cross-bar enable for null modem

operation through BMC to LAN.

A8 SCL3 EMP_INUSE_L input This status signal from the front panel

indicates that something is plugged into

Serial 2 RJ45.

C9 SDA4 PB3_I2C_3V_SDA bidir BMC Private I2C Bus 3 - data

D9 SCL4 PB3_I2C_3V_SCL bidir BMC Private I2C Bus 3 - clock

B9 SDA5 PB4_I2C_3VSB_SDA bidir BMC Private I2C Bus 4 - data

A9 SCL5 PB4_I2C_3VSB_SCL bidir BMC Private I2C Bus 4 - clock

C1 TMS BMC_TMS input Sahalee JTAG signal

D2 TCK BMC_TCK input Sahalee JTAG signal

B2 TDI BMC_TDI input Sahalee JTAG signal

B1 TDO BMC_TDO output Sahalee JTAG signal

C2 TRST* BMC_TRST_L input Sahalee JTAG signal

D3 TEST_MODE* PULLUP input Sahalee test mode signal, should be pulled

high.