Intel® Server Board SE7501WV2 TPS Server Management

Revision 1.0

Intel reference number C25653-001

55

5.1 Sahalee Baseboard Management Controller (BMC)

The Sahalee BMC contains a 32-bit RISC processor core and associated peripherals used to

monitor the system for critical events. The Sahalee BMC, packaged in a 156-pin BGA, monitors

all power supplies, including those generated by the external power supplies and those

regulated locally on the server board. The Sahalee BMC also monitors SCSI termination

voltage, fan tachometers for detecting a fan failure, and system temperature. Temperature is

measured on each of the processors and at locations on the server board away from the fans.

When any monitored parameter is outside of defined thresholds, the Sahalee BMC logs an

event in the system event log.

Management controllers and sensors communicate on the I

2

C*-based Intelligent Platform

Management Bus (IPMB). Attached to one of its private I

2

C bus is the Heceta5, an ADM1026

device, which is a versatile systems monitor ASIC. Some of its features include:

• Analog measurement channels

• Fan speed measurement channels

• General-Purpose Logic I/O pins

• Remote temperature measurement

• On-chip temperature sensor

• Chassis intrusion detect

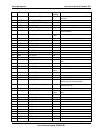

The following table details the inputs/outputs of the Sahalee BMC as used in the SE7501WV2

server system.

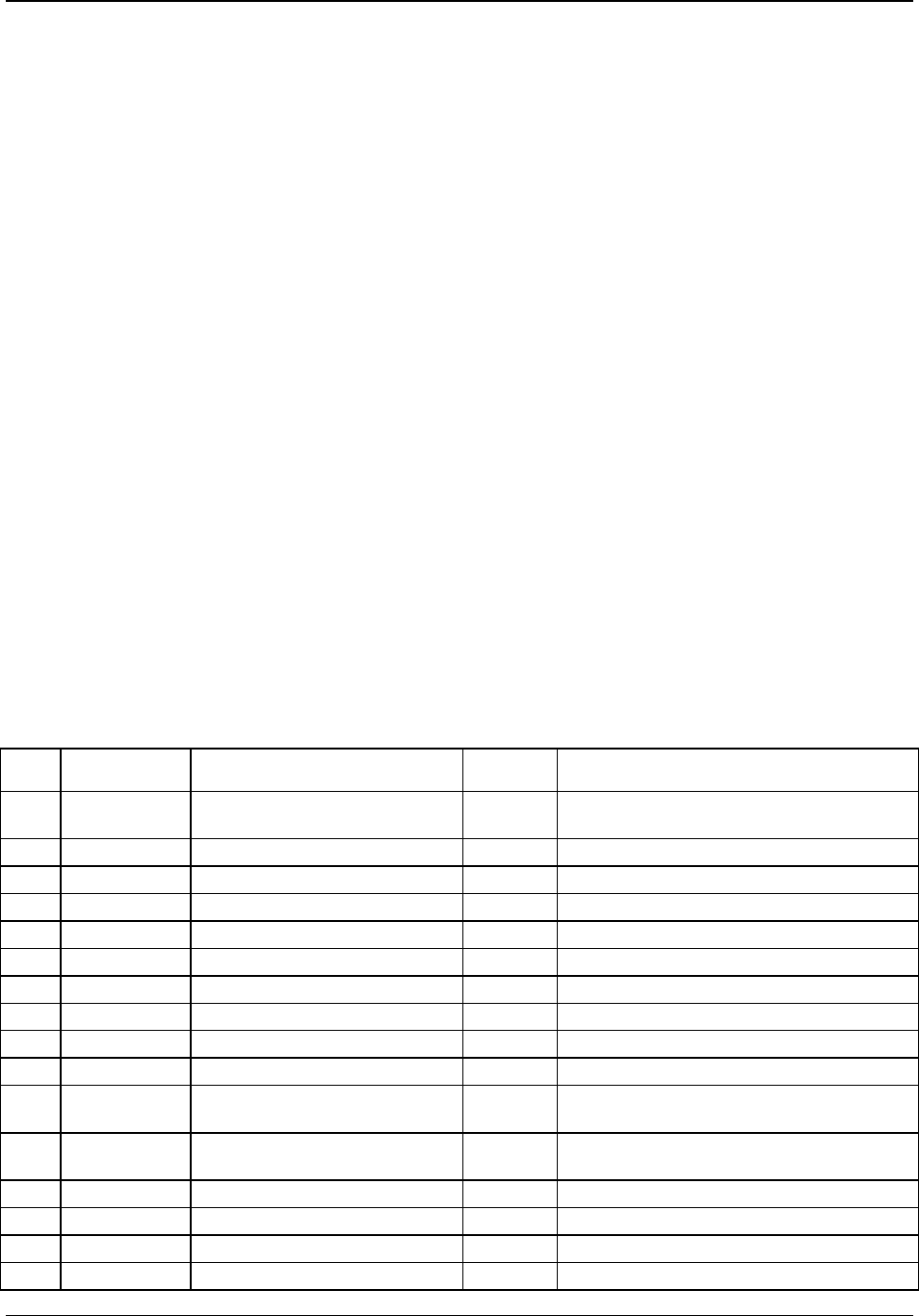

Table 21. BMC Pinout

Pin # Pin Name Signal Type/

Config

Description

D1 RST* BMC_RST_DLY_L input Delayed version of A/C power-on reset

signal from Heceta5

M7 XTAL2 TP_SAH_XTAL2 output Unused

P8 XTAL1 CLK_40M_BMC input 40MHz clock from SIO

C3 VREF VREF_A_BMC_2P5V input +2.5v reference voltage from Heceta5

A3 A2D0 TP_BMC_16 input

B4 A2D1 TP_TIC2_A2D<1> input

C4 A2D2 TP_BMC_15 input

A4 A2D3 TP_BMC_A2D<3> input

D5 A2D4 TP_BMC_A2D<4> input

B5 A2D5 TP_BMC_A2D<5> input

C5 A2D6 PV_TERMPWR_SCWB_SCALE

D

input SCSI Wide B Terminator voltage monitor.

A5 A2D7 PV_TERMPWR_SCWA_SCALE

D

input SCSI Wide A Terminator voltage monitor.

J13 XINT0 RST_PWRGD_PS input Power Good signal from power supply

K11 XINT1 ICH3_SLP_S5_L input Sleep S5 signal from chipset ICH3

K12 XINT2 ICH3_SLP_S1_L input Sleep S1 signal from ICH3.

K14 XINT3 ZZ_FRB3_TIMER_HALT_L input