Intel® Server Board SE7501WV2 TPS Server Management

Revision 1.0

Intel reference number C25653-001

57

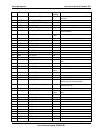

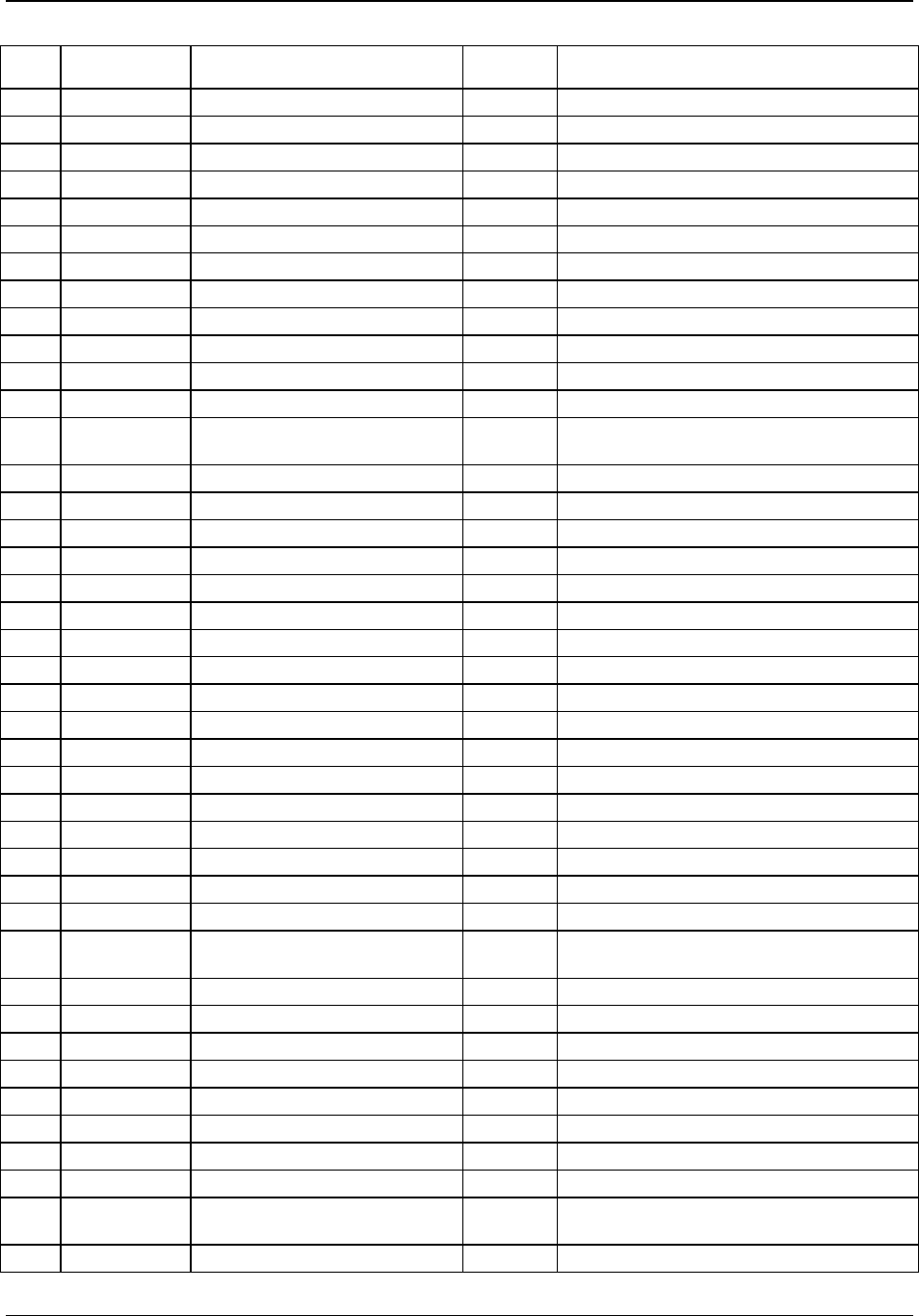

Pin # Pin Name Signal Type/

Config

Description

M2 ADDR8 BMC_A<8> output

M3 ADDR9 BMC_A<9> output

L2 ADDR10 BMC_A<10> output

L3 ADDR11 BMC_A<11> output

L1 ADDR12 BMC_A<12> output

K4 ADDR13 BMC_A<13> output

K2 ADDR14 BMC_A<14> output

K3 ADDR15 BMC_A<15> output

K1 ADDR16 BMC_A<16> output

J2 ADDR17 BMC_A<17> output

J3 ADDR18 BMC_A<18> output

J1 ADDR19 BMC_A<19> output

H4 ADDR20 BMC_A<20> output Only used if a 16M flash part is populated,

then unstuff pdn

H2 ADDR21 BMC_A<21> output

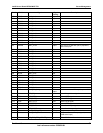

P10 DATA0 BMC_D<0> bidir

L9 DATA1 BMC_D<1> bidir

N9 DATA2 BMC_D<2> bidir

M9 DATA3 BMC_D<3> bidir

P9 DATA4 BMC_D<4> bidir

L8 DATA5 BMC_D<5> bidir

N8 DATA6 BMC_D<6> bidir

P7 DATA7 BMC_D<7> bidir

N7 DATA8 BMC_D<8> bidir

M6 DATA9 BMC_D<9> bidir

P6 DATA10 BMC_D<10> bidir

N6 DATA11 BMC_D<11> bidir

L5 DATA12 BMC_D<12> bidir

M5 DATA13 BMC_D<13> bidir

P5 DATA14 BMC_D<14> bidir

N5 DATA15 BMC_D<15> bidir

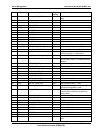

J14 BAUD BMC_IRQ_SMI_L OD

output

Need to connect to SMI capable pin at ICH3

J12 RI* SPB_RI_L input Serial 2 ring indicate signal.

F14 DTR0* SPB_DTR_L output Serial 2 DTR signal.

F12 DCD0* SPB_DCD_L input Serial 2 DCD signal.

F13 CTS0* SPB_CTS_L input Serial 2 CTS signal.

F11 RTS0* SPB_RTS_L output Serial 2 RTS signal.

E12 RX0 SPB_SIN input Serial 2 serial input signal

E13 TX0 SPB_SOUT output Serial 2 serial output signal

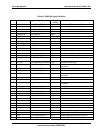

J11 DTR1* BMC_LATCH_OE_L TP output Enables output of expansion latch

H13 DCD1* BMC_ICMB_RX input ICMB receive data interrupt signal (same as

ICMB serial input)

H14 CTS1* NSI_BMC_FRC_UPDATE_L input Forces BMC to run from boot block code.