Server Management Intel® Server Board SE7501WV2 TPS

Revision 1.0

Intel reference number C25653-001

56

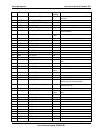

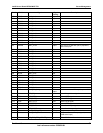

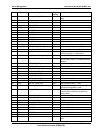

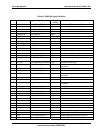

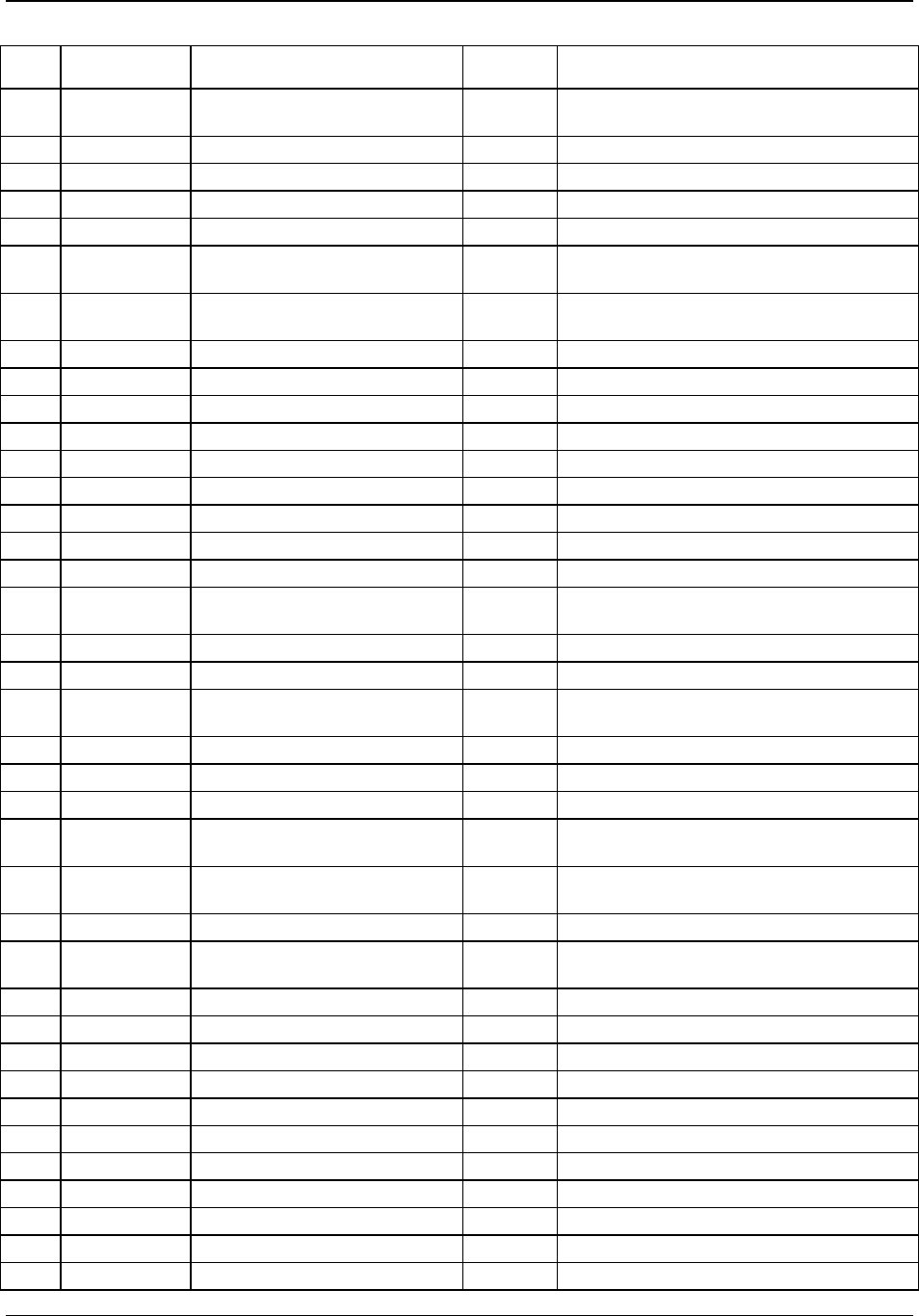

Pin # Pin Name Signal Type/

Config

Description

K13 XINT4 NIC1_SMBALERT_L input SMBus Alert Signal from NIC1 (82546EB)

TCO port

L14 XINT5 ICH3_SMI_BUFF_L input

L12 XINT6 BMC_PCU12_PROCHOT_L input Prochot signal. Can be Polled or Interrupt

L13 XINT7 BMC_NMI_L OD out/in NMI signal, monitored or asserted by BMC

D4 LPCRST* RST_PCIRST_L input Buffered ICH3 PCIRST

E2 LPCPD* ICH3_SUS_STAT_L input Signal used to 3-state LPC outputs to

prevent leakage

B11 LSMI* BMC_SCI_L OD

output

SCI output signal

F4 LDRQ* LPC_DRQ_L<0> output

G2 SYSIRQ IRQ_SIO_SERIRQ output Connected to SIO GPIO06/XIRQ input

F3 LFRAME* LPC_FRAME_L input

G1 LCLK CLK_33M_BMC input

F1 LAD0 LPC_AD<0> bidir

F2 LAD1 LPC_AD<1> bidir

E3 LAD2 LPC_AD<2> bidir

E1 LAD3 LPC_AD<3> bidir

G3 CS1* BMC_SRAM_CE_L output Chip enable for external SRAM

H1 CS0* BMC_CS0_L output Chip enable for BMC flash/ memory mapped

latch

M10 WE* BMC_WE_L output Flash/SRAM write enable

N10 OE* BMC_OE_L output Flash/SRAM output enable

M14 BW8* BMC_SLP_BTN_L OD

output

Sleep input to ICH3

M13 IOCHRDY FP_RST_BTN_L input Reset button signal from front panel

N14 BALE FP_NMI_BTN_L input NMI button signal from front panel

P13 MEMR* FP_ID_BTN_L input System ID signal from front panel

N13 MEMW* FP_SLP_BTN_L input Sleep button signal from front panel. For ref

chassis support. (Not supported)

M12 IOR* BMC_SECURE_MODE_KB input Secure mode signal from SIO keyboard

controller (pin 12)

N12 IOW* FP_PWR_BTN_L input Power button signal from front panel

P12 SBHE* BMC_SBHE_L OD

output

High byte enable to external SRAM and

flash

M11 CE2* RST_VRM_DIS_L TP output Disables CPU VRM.

N11 CE1* BMC_VID_BLANK_L TP output Disables Hsync and Vsync video buffers

P11 REG* BMC_CLR_CMOS_L TP output Clear CMOS signal asserted by BMC.

L4 ADDR0 BMC_A<0> output

P4 ADDR1 BMC_A<1> output

M4 ADDR2 BMC_A<2> output

N4 ADDR3 BMC_A<3> output

P3 ADDR4 BMC_A<4> output

P2 ADDR5 BMC_A<5> output

N2 ADDR6 BMC_A<6> output

N1 ADDR7 BMC_A<7> output