Intel® Server Board SE7501WV2 TPS Server Management

Revision 1.0

Intel reference number C25653-001

61

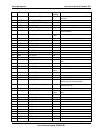

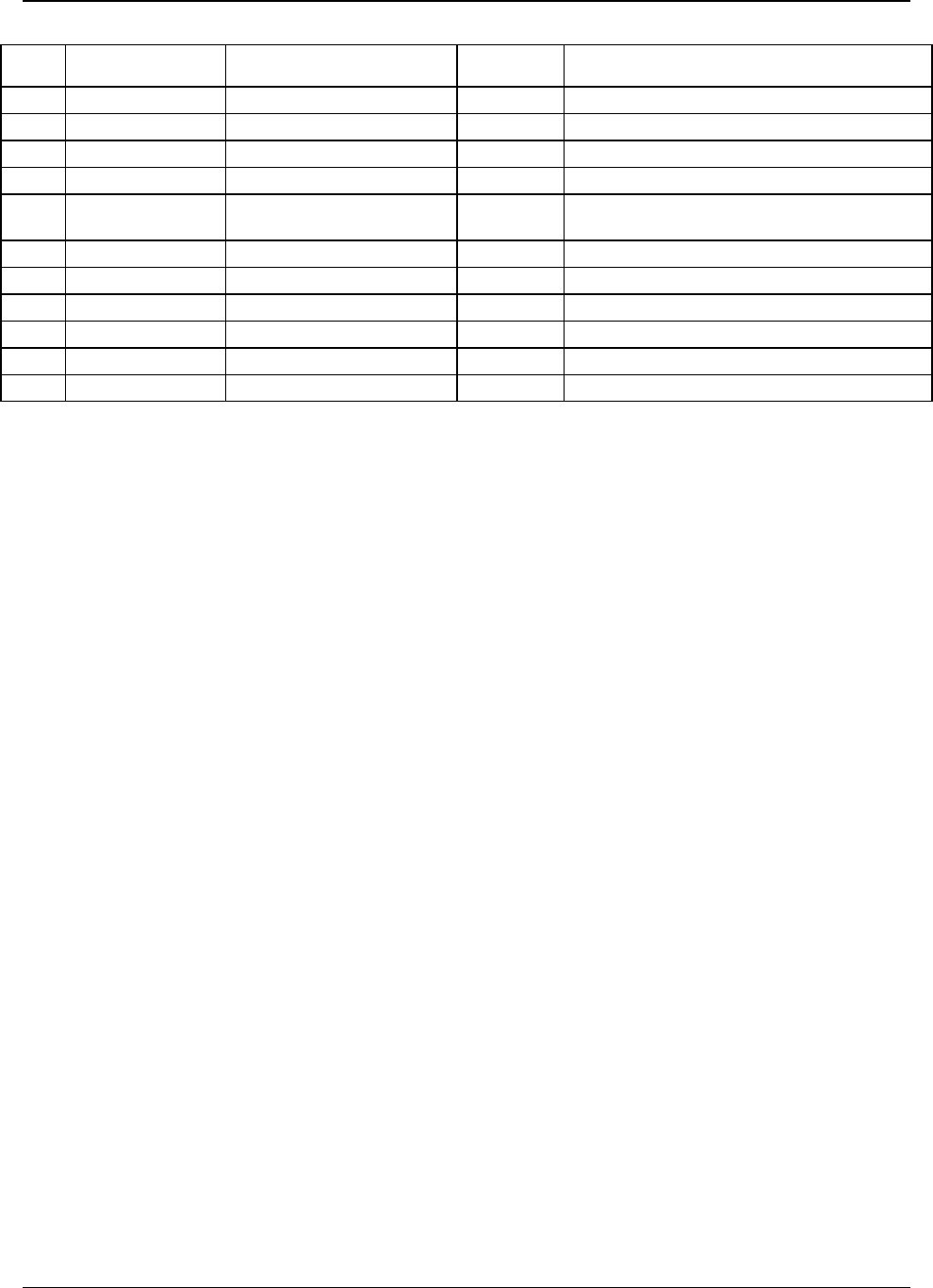

Pin # Pin Name Signal Type/

Config

Description

38 AIN3 P2V5 input Baseboard P2V5 monitor

39 AIN2 P5V_STBY_SCALED input External attenuator=1k/(1k+1k)=0.5

40 AIN1 P1V8_STBY input Baseboard P1V8_STBY monitor

41 AIN0 P3V3_VAUX input External attenuator=499k/(499+365~=0.58

42 THERM*/GPIO16 TP_HEC5_GPIO16 gpio This pin does not yet have a specified

connection.

43 GPIO15 BMC_CPU2_THRMTRIP_L input Processor Thermal Trip signal from CPU2

44 GPIO14 BMC_CPU1_THRMTRIP_L input Processor Thermal Trip signal from CPU1

46 GPIO13 VID_CPU1<3> input

45 GPIO12 VID_CPU1<4> input

47 GPIO11 VID_CPU1<2> input

48 GPIO10 VID_CPU1<1> input

5.1.1 Fault Resilient Booting

The Sahalee BMC implements Fault Resilient Booting (FRB) levels 1, 2, and 3. If the default

bootstrap processor (BSP) fails to complete the boot process, FRB attempts to boot using an

alternate processor.

• FRB level 1 is for recovery from a BIST failure detected during POST. This FRB

recovery is fully handled by BIOS code.

• FRB level 2 is for recovery from a watchdog timeout during POST. The watchdog timer

for FRB level 2 detection is implemented in the Sahalee BMC.

• FRB level 3 is for recovery from a watchdog timeout on hard reset or power-up. The

Sahalee BMC provides hardware functionality for this level of FRB.

5.1.1.1 FRB-1

In a multiprocessor system, the BIOS registers the application processors in the MP table and

the ACPI tables. When started by the BSP, if an AP fails to complete initialization within a

certain time, it is assumed nonfunctional. If the BIOS detects that an application processor has

failed BIST or is nonfunctional, it requests the BMC to disable that processor. The BMC then

generates a system reset while disabling the processor; the BIOS will not see the bad processor

in the next boot cycle. The failing AP is not listed in the MP table (refer to the Multi-Processor

Specification, Rev. 1.4), nor in the ACPI APIC tables, and is invisible to the operating system. If

the BIOS detects that the BSP has failed BIST, it sends a request to the BMC to disable the

present processor. If there is no alternate processor available, the BMC beeps the speaker and

halts the system. If BMC can find another processor, BSP ownership is transferred to that

processor via a system reset.

5.1.1.2 FRB-2

The second watchdog timer (FRB-2) in the BMC is set for approximately 6 minutes by BIOS and

is designed to guarantee that the system completes BIOS POST. The FRB-2 timer is enabled

before the FRB-3 timer is disabled to prevent any “unprotected” window of time.