Functional Architecture Intel® Server Board SE7501WV2 TPS

Revision 1.0

Intel reference number C25653-001

32

3.2.4.5 APIC

The ICH3-S integrates an APIC that is used to distribute 24 interrupts.

3.2.4.6 Power Management

One of the embedded functions of the ICH3-S is a power management controller. The

SE7501WV2 server board uses this to implement ACPI-compliant power management features.

The SE7501WV2 supports sleep states S0, S1, S4, and S5.

3.3 Super I/O

The National Semiconductor* PC87417 Super I/O device contains all of the necessary circuitry

to control two serial ports, one parallel port, one floppy disk, and one PS/2-compatible keyboard

and mouse. The SE7501WV2 server board supports the following features:

• GPIOs

• Two serial ports

• Floppy

• Keyboard and mouse through one PS/2 connector

• Wake up control

3.3.1 GPIOs

The National Semiconductor* PC87417 Super I/O provides nine general-purpose input/output

pins that the SE7501WV2 server board utilizes. The following table identifies the pin and the

signal name used in the schematic:

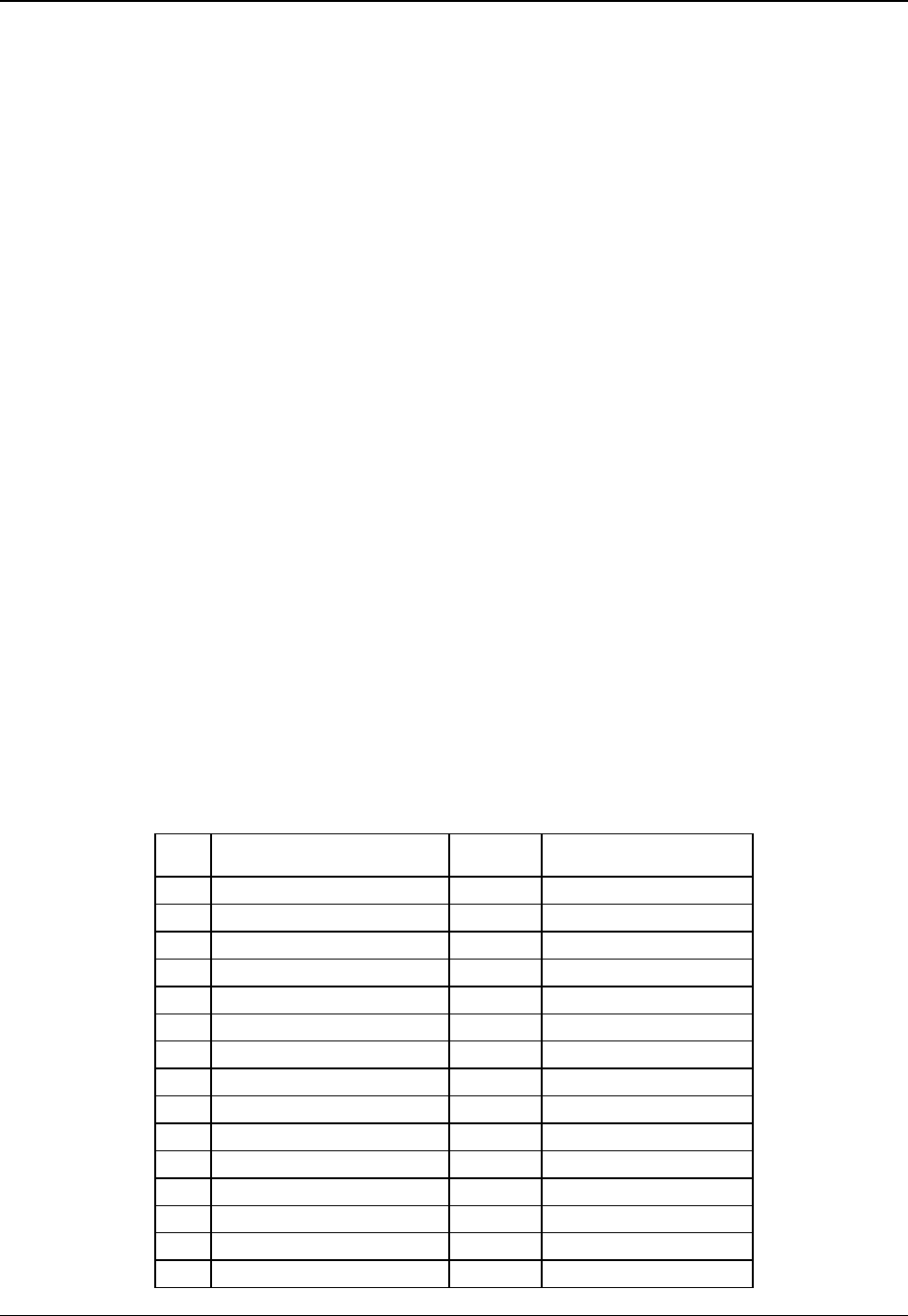

Table 6. Super I/O GPIO Usage Table

Pin Name IO/GPIO

Intel

®

Server Board

SE7501WV2 Use

124 GPIO00/CLKRUN_L I/O TP

125 GPIO01/KBCLK I/O KB_CLK

126 GPIO02/KBDAT I/O KB_DAT

127 GPIO03/MCLK I/O MS_CLK

128 GPIO04/MDAT I/O MS_DAT

9 GPIO05/XRDY I/O TP

10 GPIO06/XIRQ I/O BMC_SYSIRQ

13 GPIO07/HFCKOUT I/O SIO_CLK_40M_BMC

1 GPIOE10/XA11 I/O,I(E)1 XBUS_A<11>

2 GPIOE11/XA10 I/O,I(E)1 XBUS_A<10>

3 GPIOE12/XA9 I/O,I(E)1 XBUS_A<9>

4 GPIOE13/XA8 I/O,I(E)1 XBUS_A<8>

5 GPIOE14/XA7 I/O,I(E)1 XBUS_A<7>

6 GPIOE15/XA6 I/O,I(E)1 XBUS_A<6>

7 GPIOE16/XA5 I/O,I(E)1 XBUS_A<5>