Product Preview DS21Q55

136 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

22.2.1 FIFO Control

Control of the transmit and receive FIFOs is accomplished via the FIFO control (HxFC). The FIFO

control register sets the watermarks for both the transmit and receive FIFO. Bits 3–5 set the transmit low

watermark and the lower 3 bits set the receive high watermark.

When the transmit FIFO empties below the low watermark, the TLWM bit in the appropriate HDLC

status register SR6 or SR7 will be set. TLWM is a real-time bit and will remain set as long as the transmit

FIFO’s read pointer is below the watermark. If enabled, this condition can also cause an interrupt via the

*INT pin.

When the receive FIFO fills above the high watermark, the RHWM bit in the appropriate HDLC status

register will be set. RHWM is a real-time bit and will remain set as long as the receive FIFO’s write

pointer is above the watermark. If enabled, this condition can also cause an interrupt via the *INT pin.

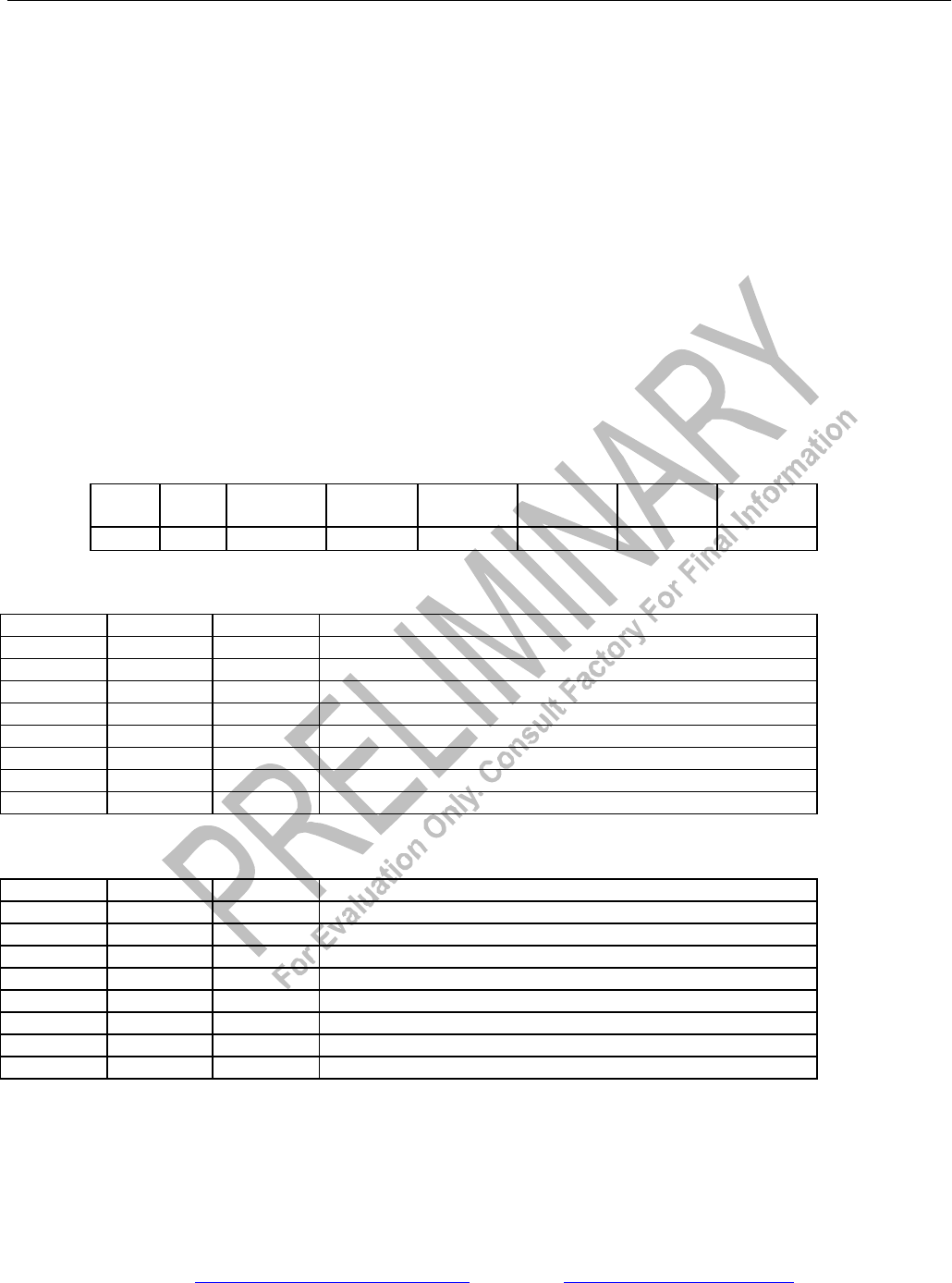

Register Name: H1FC, H2FC

Register Description: HDLC # 1 FIFO Control, HDLC # 2 FIFO Control

Register Address: 91h, A1h

Bit # 7 6 5 4 3 2 1 0

Name - - TFLWM2 TFLWM

1

TFLWM0 RFHWM2

RFHWM1

RFHWM0

Default 0 0 0 0 0 0 0 0

Bits 0 to 2/Receive FIFO High Watermark Select (RFHWM0 to RFHWM2).

RFHWM2 RFHWM1

RFHWM0

RECEIVE FIFO WATERMARK (BYTES)

0 0 0 4

0 0 1 16

0 1 0 32

0 1 1 48

1 0 0 64

1 0 1 80

1 1 0 96

1 1 1 112

Bits 3 to 5/Transmit FIFO Low Watermark Select (TFLWM0 to TFLWM2).

TFLWM2 TFLWM1 TFLWM0 TRANSMIT FIFO WATERMARK (BYTES)

0 0 0 4

0 0 1 16

0 1 0 32

0 1 1 48

1 0 0 64

1 0 1 80

1 1 0 96

1 1 1 112

Bit 6/Unused, must be set to zero for proper operation.

Bit 7/Unused, must be set to zero for proper operation.