Product Preview DS21Q55

75 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

13.2 Path Code Violation Count Register (PCVCR)

T1 Operation

The path-code violation-count register records either Ft, Fs, or CRC6 errors in T1 frames. When the

receive side of a framer is set to operate in the T1 ESF framing mode, PCVCR will record errors in the

CRC6 code words. When set to operate in the T1 D4 framing mode, PCVCR will count errors in the Ft

framing bit position. Via the ERCNT.2 bit, a framer can be programmed to also report errors in the Fs

framing bit position. The PCVCR will be disabled during receive loss of synchronization (RLOS = 1)

conditions. See Table 15-3 for a detailed description of exactly what errors the PCVCR counts.

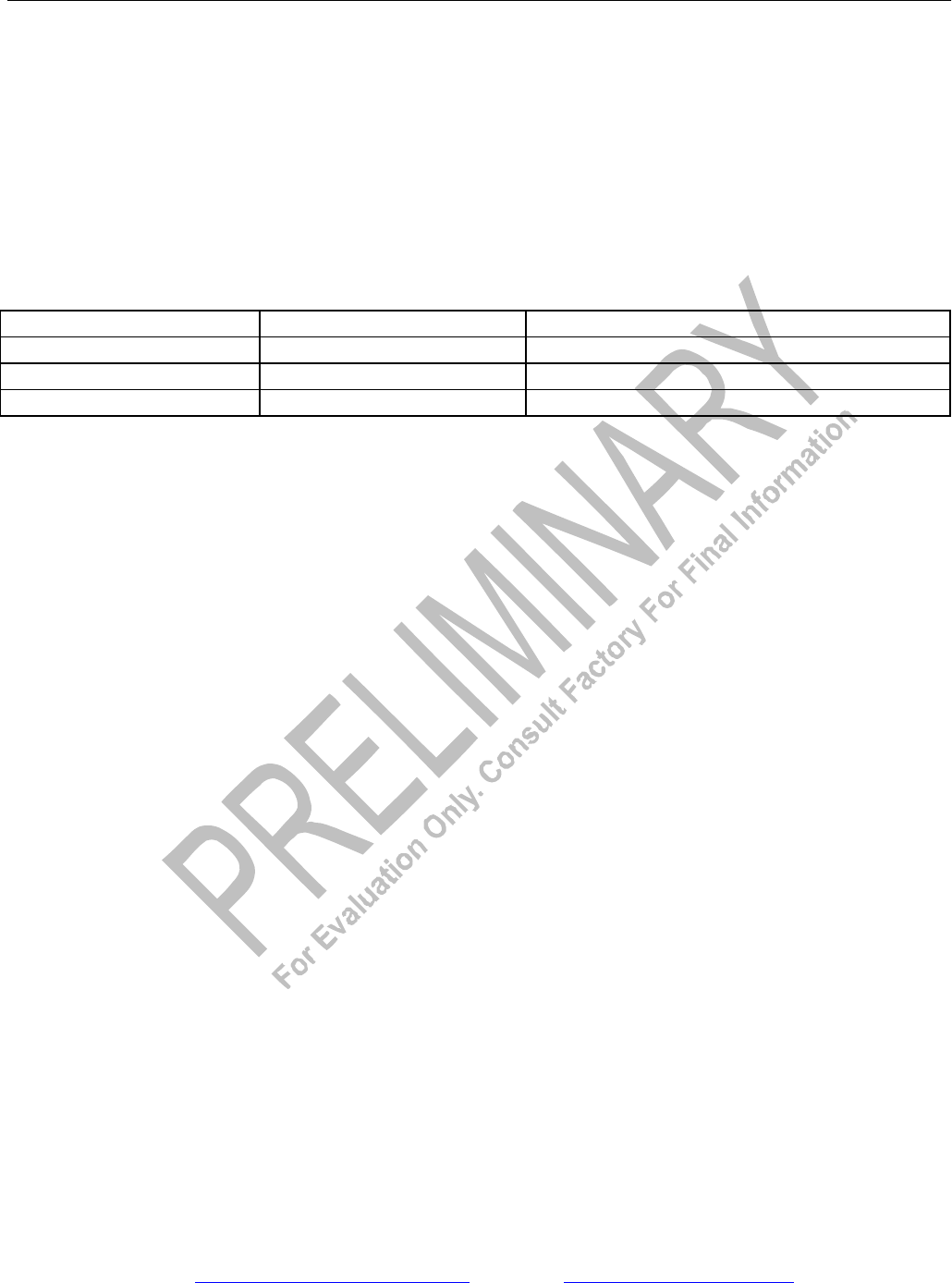

T1 PATH CODE VIOLATION COUNTING ARRANGEMENTS Table 15-3

FRAMING MODE COUNT Fs ERRORS? WHAT IS COUNTED IN THE PCVCRs

D4 No Errors in the Ft Pattern

D4 Yes Errors in Both the Ft and Fs Patterns

ESF Don’t Care Errors in the CRC6 Code Words

E1 Operation

The PCVCR records CRC4 errors. Since the maximum CRC4 count in a one-second period is 1000, this

counter cannot saturate. The counter is disabled during loss of sync at either the FAS or CRC4 level; it

will continue to count if loss of multiframe sync occurs at the CAS level.

The PCVCR1 is the most significant word and PCVCR2 is the least significant word of a 16-bit counter

that records path violations (PVs).