Product Preview DS21Q55

220 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

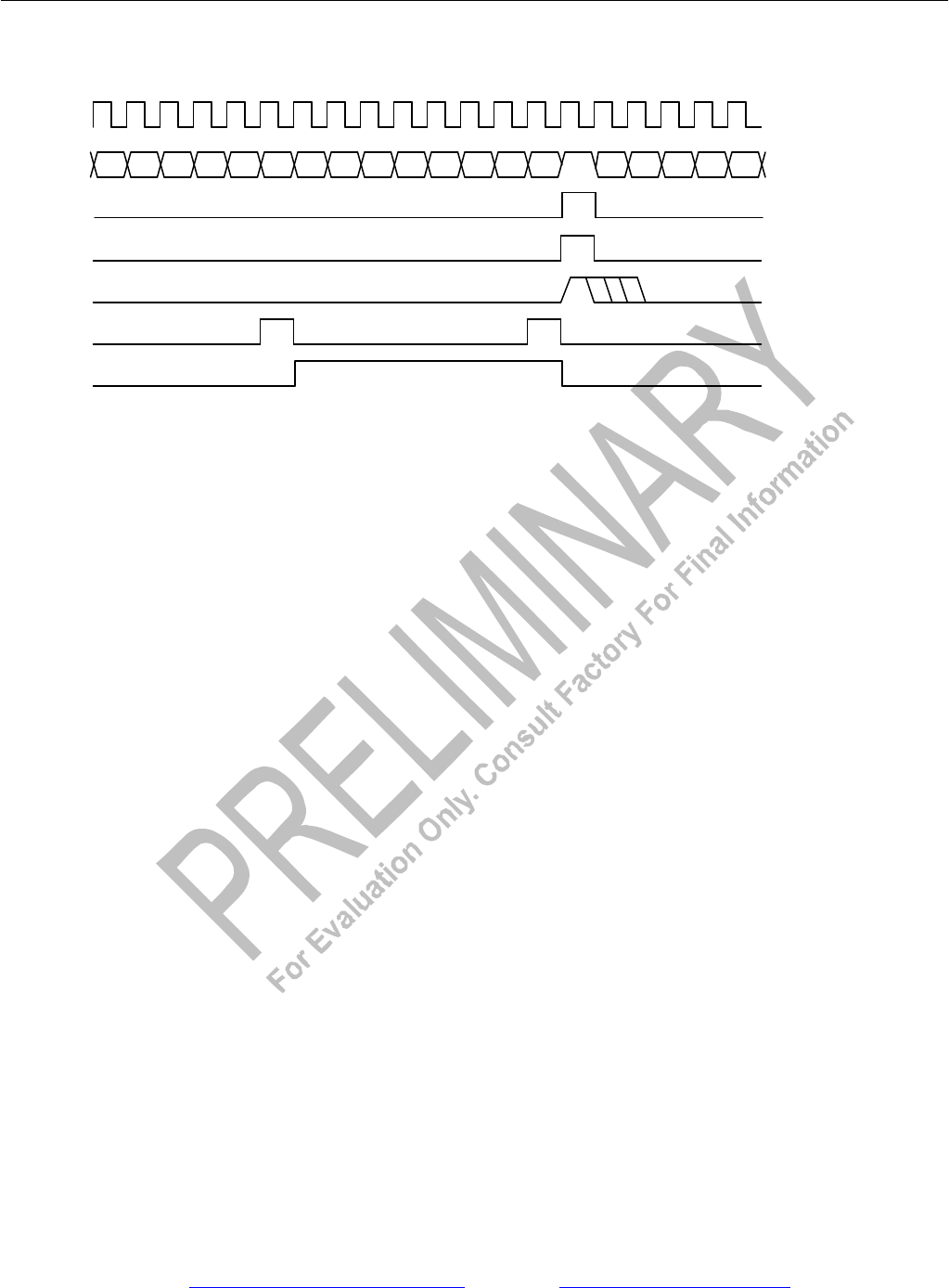

RECEIVE SIDE BOUNDARY TIMING, RSYSCLK = 1.544MHz (With Elastic

Store Enabled) Figure 35-13

NOTES:

1) Data from the E1 channels 1, 5, 9, 13, 17, 21, 25, and 29 is dropped (channel 2 from the E1 link is

mapped to channel 1 of the T1 link, etc.) and the F-bit position is added (forced to one).

2) RSYNC in the output mode (IOCR1.4 = 0).

3) RSYNC in the input mode (IOCR1.4 = 1).

4) RCHBLK is programmed to block channel 24.

RSER

CHANNEL 23/31 CHANNEL 24/32 CHANNEL 1/2

RCHCLK

RCHBLK

RSYSCLK

RSYNC

2

3

RSYNC

1

RMSYNC

LSB

F

MSB

MSB

LSB

4