Product Preview DS21Q55

143 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

Register Name: INFO5, INFO6

Register Description: HDLC #1 Information Register

HDLC #2 Information Register

Register Address: 2Eh, 2Fh

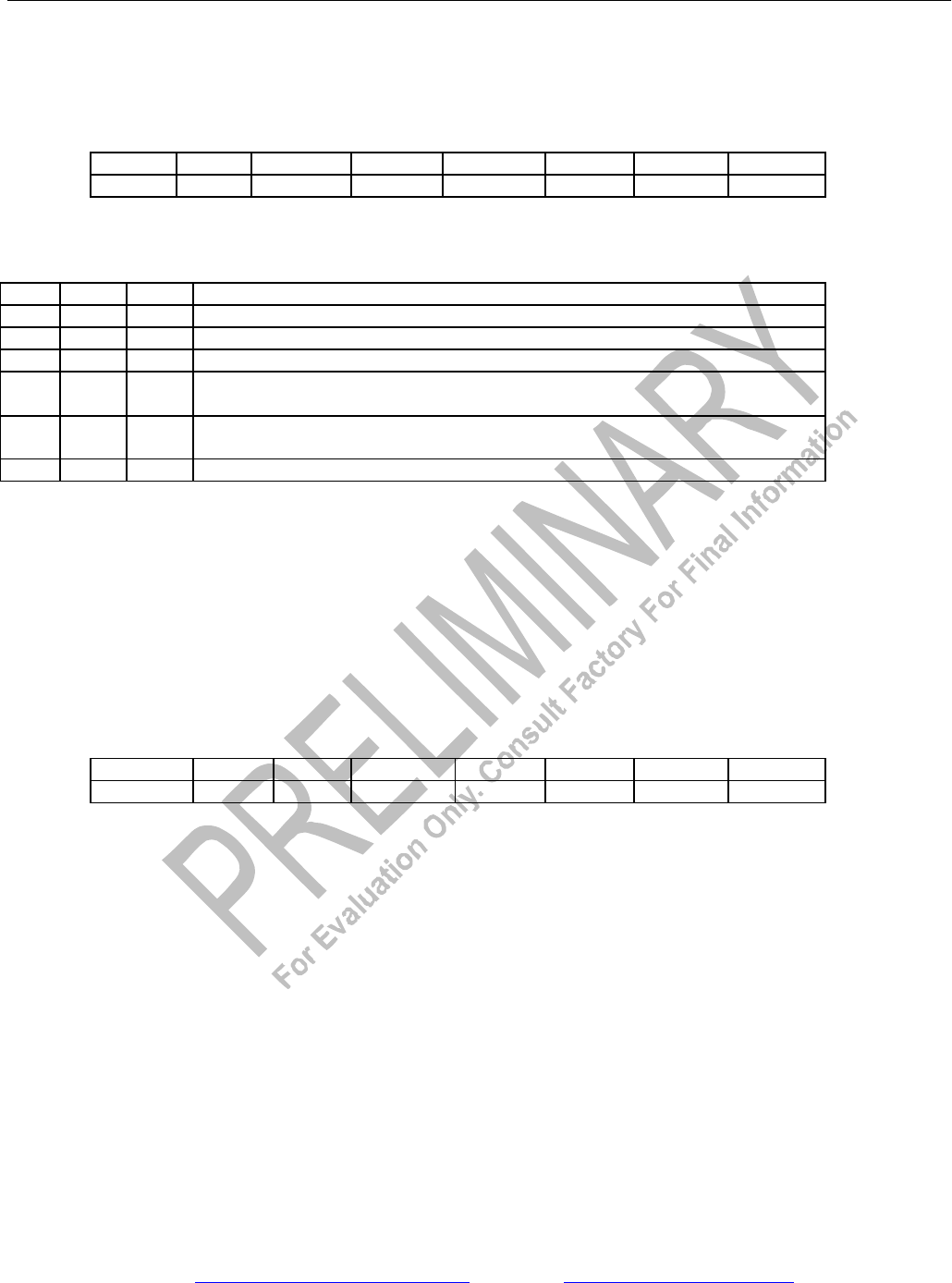

Bit # 7 6 5 4 3 2 1 0

Name - - TEMPTY TFULL REMPTY PS2 PS1 PS0

Default 0 0 0 0 0 0 0 0

Bits 0 to 2/Receive Packet Status (PS0 to PS2). These are real-time bits indicating the status as of the last read of the receive

FIFO.

PS2 PS1 PS0 PACKET STATUS

0 0 0 In Progress: End of message has not yet been reached

0 0 1 Packet OK: Packet ended with correct CRC code word

0 1 0 CRC Error: A closing flag was detected, preceded by a corrupt CRC code word

0 1 1

Abort: Packet ended because an abort signal was detected (seven or more ones in

a row)

1 0 0

Overrun: HDLC controller terminated reception of packet because receive FIFO

is full

1 0 1 Message Too Short: Three or fewer bytes including CRC

Bit 3/Receive FIFO Empty (REMPTY). A real-time bit that is set high when the receive FIFO is empty.

Bit 4/Transmit FIFO Full (TFULL). A real-time bit that is set high when the FIFO is full.

Bit 5/Transmit FIFO Empty (TEMPTY). A real-time bit that is set high when the FIFO is empty.

Register Name: INFO4

Register Description: HDLC Event Information Register #4

Register Address: 2Dh

Bit # 7 6 5 4 3 2 1 0

Name H2UDR H2OBT H1UDR H1OBT

Default 0 0 0 0 0 0 0 0

Bit 0/HDLC #1 Opening Byte Event (H1OBT). Set when the next byte available in the receive FIFO is the first byte of a

message.

Bit 1/HDLC #1 Transmit FIFO Underrun Event (H1UDR). Set when the transmit FIFO empties out without having seen

the TMEND bit set. An abort is automatically sent. This bit is latched and will be cleared when read.

Bit 2/HDLC #2 Opening Byte Event (H2OBT). Set when the next byte available in the receive FIFO is the first byte of a

message.

Bit 3/HDLC #2 Transmit FIFO Underrun Event (H2UDR). Set when the transmit FIFO empties out without having seen

the TMEND bit set. An abort is automatically sent. This bit is latched and will be cleared when read.