Product Preview DS21Q55

29 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

3.9 Package

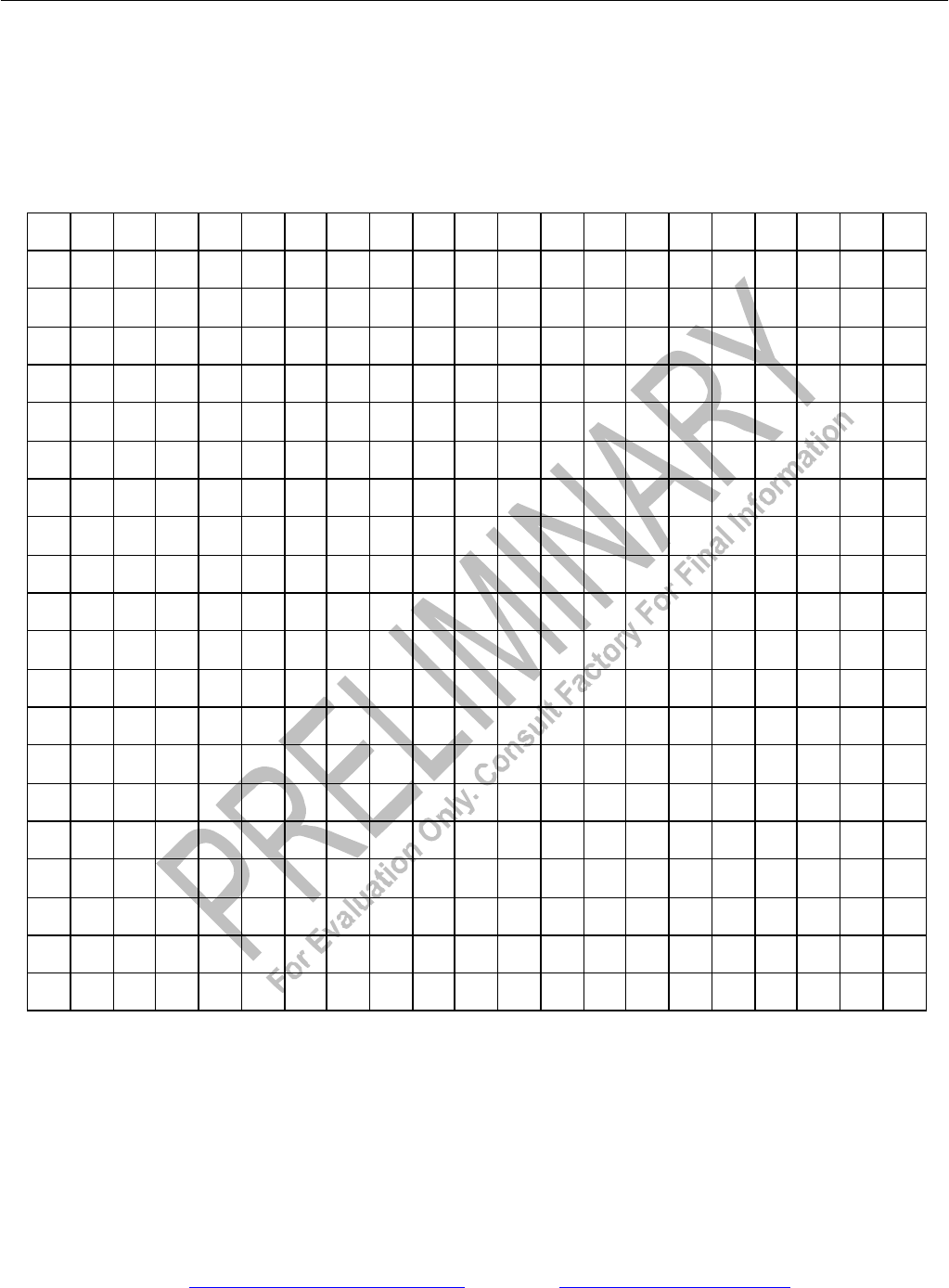

DS21Q55 Pin DIAGRAM, 27mm BGA Figure 5-1

The diagram shown below is the lead pattern that will be placed on the target PCB. This is the same pattern that would be seen

as viewed from the top.

1 2 3 4 5 6 7 8 9 10

11

12 13

14

15

16 17

18

19 20

A

rnegi

3

rfsync

3

rlink

3

rclki

3

dvss

3

esibs1

3

tclko

3

tposi

3

dvdd

3

tsig

3

tsysclk

3

rlclk

2

rlink

2

cs

2*

rclki

2

rposo

2

dvss

2

tchclk

2

tsysclk

2

dvss

2

B

rposo

3

rposi

3

dvdd

3

rclko

3

cs

3*

dvdd

3

dvss

3

tchclk

3

dvss

3

tclk

3

dvss

2

dvdd

2

rclk

2

rposi

2

rnego

2

rsig

2

esibs1

2

tssync

2

tclk

2

tnego

2

C

rsig

3

rnego

3

eisbrd

3

dvdd

3

tvss

3

tlink

3

tsync

3

tclki

3

tposo

3

tser

3

tchblk

3

dvdd

2

eisbrd

2

rclko

2

rsigf

2

dvdd

2

tser

2

tsig

2

tposo

2

tposi

2

D

rsync

3

rsigf

3

rlclk

3

rvss

3

rvss

3

tlclk

3

esibs0

3

tnegi

3

tnego

3

tssync

3

tvdd

3

rsync

2

rnegi

2

rchclk

2

rser

2

rmsync

2

rfsync

2

dvdd

2

tclki

2

tsync

2

E

rlos

3

rser

3

rclk

3

rvdd

3

rlos

2

tclko

2

tlink

2

tlclk

2

F

rlclk

1

rmsync

3

rchclk

3

bpclk

3

rsysclk

2

esibs0

2

tnegi

2

tchblk

2

G

rsync

1

rlink

1

rsysclk

3

rchblk

3

rchblk

2

tvss

2

tvdd

2

dvdd

4

H

rsysclk

1

rlos

1

dvss

1

a5

bpclk

2

NC

rvss

2

dvss

4

J

rchclk

1

rser

1

dvdd

1

eisbrd

1

rvdd

2

rvss

2

D1/

AD1

esibs1

4

K

rsigf

1

liuc wr*

rfsync

1

cs

4*

rlclk

4

tssync

4

tser

4

L

rmsync

1

rsig

1

rnego

1

rposo

1

A1

tchclk

4

tsig

4

dvss

4

M

bpclk

1

rchblk

1

rclko

1

rclki

1

dvdd

4

rclk

4

tclk

4

dvdd

4

N

jtdi rd*

rclk

1

dvdd

1

dvss

4

tsys

clk4

tposo

4

tnego

4

P

rvdd

1

bts

cs

1*

A7/AL

E(AS)

rnegi

4

dvdd

4

tclko

4

tclki

4

R

tnegi

1

rvss

1

rnegi

1

rposI

1

rclki

4

tsync

4

tposi

4

tnegi

4

T

mclk

1

rvss

1

tnego

1

A3

rclko

4

tlclk

4

tlink

4

esibs0

4

U

int*

dvdd

1

A0

D7/

AD7

D5/

AD5

dvss

1

D3/

AD3

A6

D4/

AD4

mux

D0/

AD0

rlink

4

eisbrd

4

rchclk

4

rposo

4

tstrst

rnego

4

tvss

4

tvdd

4

tchblk

4

V

tsync

1

A2

tlclk

1

D6/

AD6

dvdd

1

tclki

1

tposo

1

A4

esibs1

1

tchclk

1

rlos

4

rsync

4

bpclk

4

rfsync

4

rposi

4

rsigf

4

NC jtrst* jtdo

rvss

4

W

tchblk

1

tvdd

1

tposi

1

tvss

1

tlink

1

esibs0

1

tclko

1

dvss

1

tser

1

tsig

1

tsysclk

1

tssync

1

jtms

rsysclk

4

D2/

AD2

rmsync

4

rser

4

rvdd

4

rvss

4

mclk

2

Y

ttip

1

tring

1

ttip

2

tring

2

ttip

3

tring

3

ttip

4

tring

4

tclk

1

rtip

1

rring

1

rchblk

4

rtip

2

rring

2

jtclk

rtip

3

rring

3

rsig

4

rtip

4

rring

4

NOTE: Locations C3, C13, J4, and U13 are used for the Extended System Information Bus (ESIB). These pin locations on the

DS21Q352, DS21Q354, DS21Q552, and DS21Q554 are connected to ground. When replacing a DS21Qx5y with a

DS21Q55B, these signals should be routed to control logic in order to gain access to the ESIB. If these pins remain connected

to ground, the ESIB function will be disabled.