Product Preview DS21Q55

154 of 248 012103

Please contact telecom.support@dalsemi.com or search http://www.maxim-ic.com for updated

information.

23.7 LIU Control Registers

Register Name: LIC1

Register Description: Line Interface Control 1

Register Address: 78h

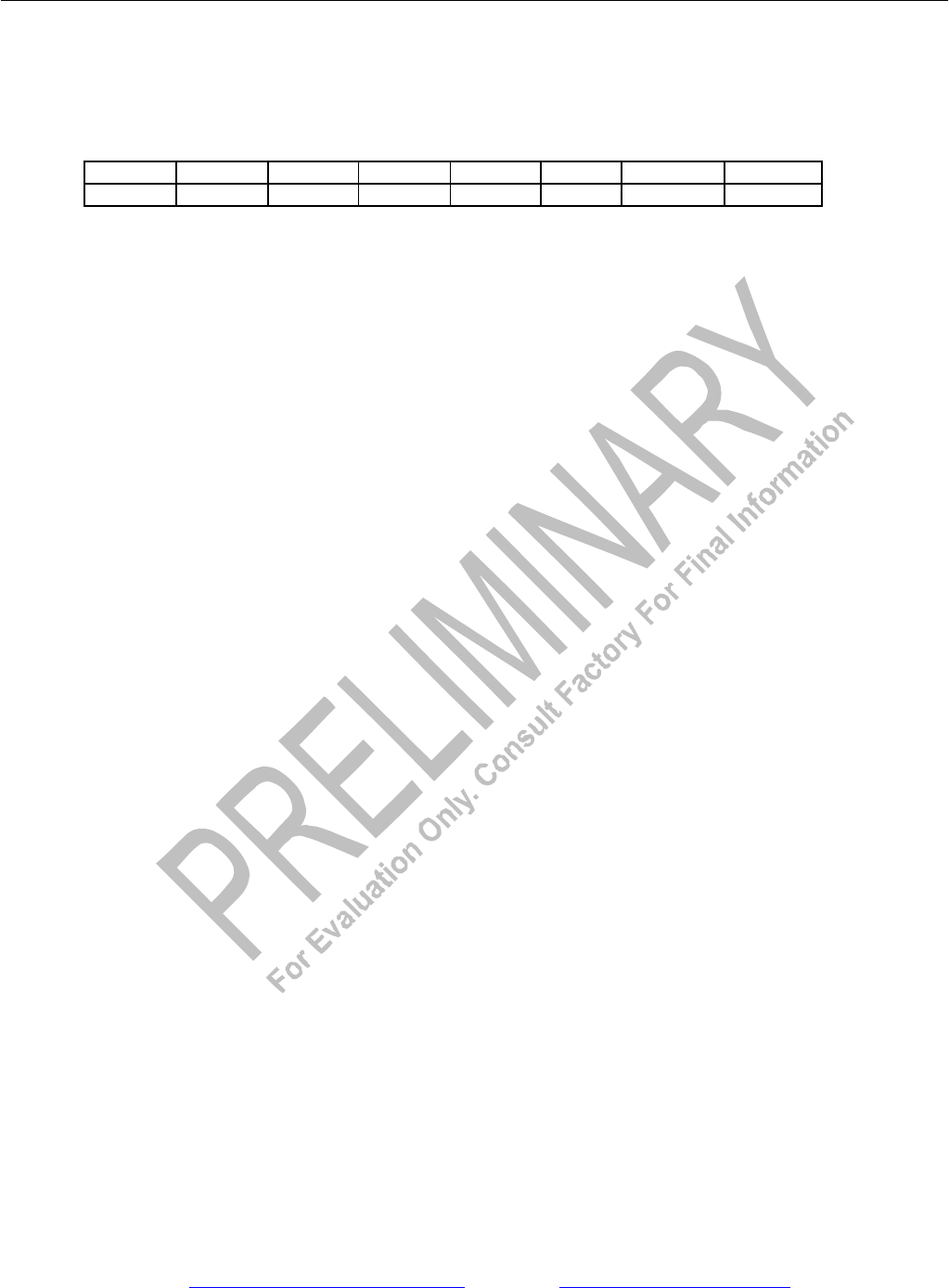

Bit # 7 6 5 4 3 2 1 0

Name L2 L1 L0 EGL JAS JABDS DJA TPD

Default 0 0 0 0 0 0 0 0

Bit 0/Transmit Power-Down (TPD).

0 = powers down the transmitter and tristates the TTIP and TRING pins

1 = normal transmitter operation

Bit 1/Disable Jitter Attenuator (DJA).

0 = jitter attenuator enabled

1 = jitter attenuator disabled

Bit 2/Jitter Attenuator Buffer Depth Select (JABDS).

0 = 128 bits

1 = 32 bits (use for delay sensitive applications)

Bit 3/Jitter Attenuator Select (JAS).

0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

Bit 4/Receive Equalizer Gain Limit (EGL). This bit controls the sensitivity of the receive equalizer.

T1 Mode: 0 = -36dB (long haul)

1 = -15dB (limited long haul)

E1 Mode: 0 = -15dB (short haul)

1 = -43dB (long haul)

Bits 5 to 7/Line Build-Out Select (L0 to L2). When using the internal termination the user needs only to select 000 for 75O

operation or 001 for 120O operation below. This selects the proper voltage levels for 75O or 120O operation. Using TT0 and

TT1 of the LICR4 register, users can then select the proper internal source termination. Line build-outs 100 and 101 are for

backwards compatibility with older products only.