146 www.xilinx.com Development System Reference Guide

Chapter 7: MAP

R

This command creates a back-annotated simulation netlist using the logical-to-physical

cross-reference file named mapped.ngm. This cross-reference file contains information

about the logical design netlist, and the back-annotated simulation netlist (mapped.nga) is

actually a back-annotated version of the logical design. However, if MAP makes a physical

error, for example, implements an Active Low function for an Active High function, this

error will not be detected in the mapped.nga file and will not appear in the simulation

netlist.

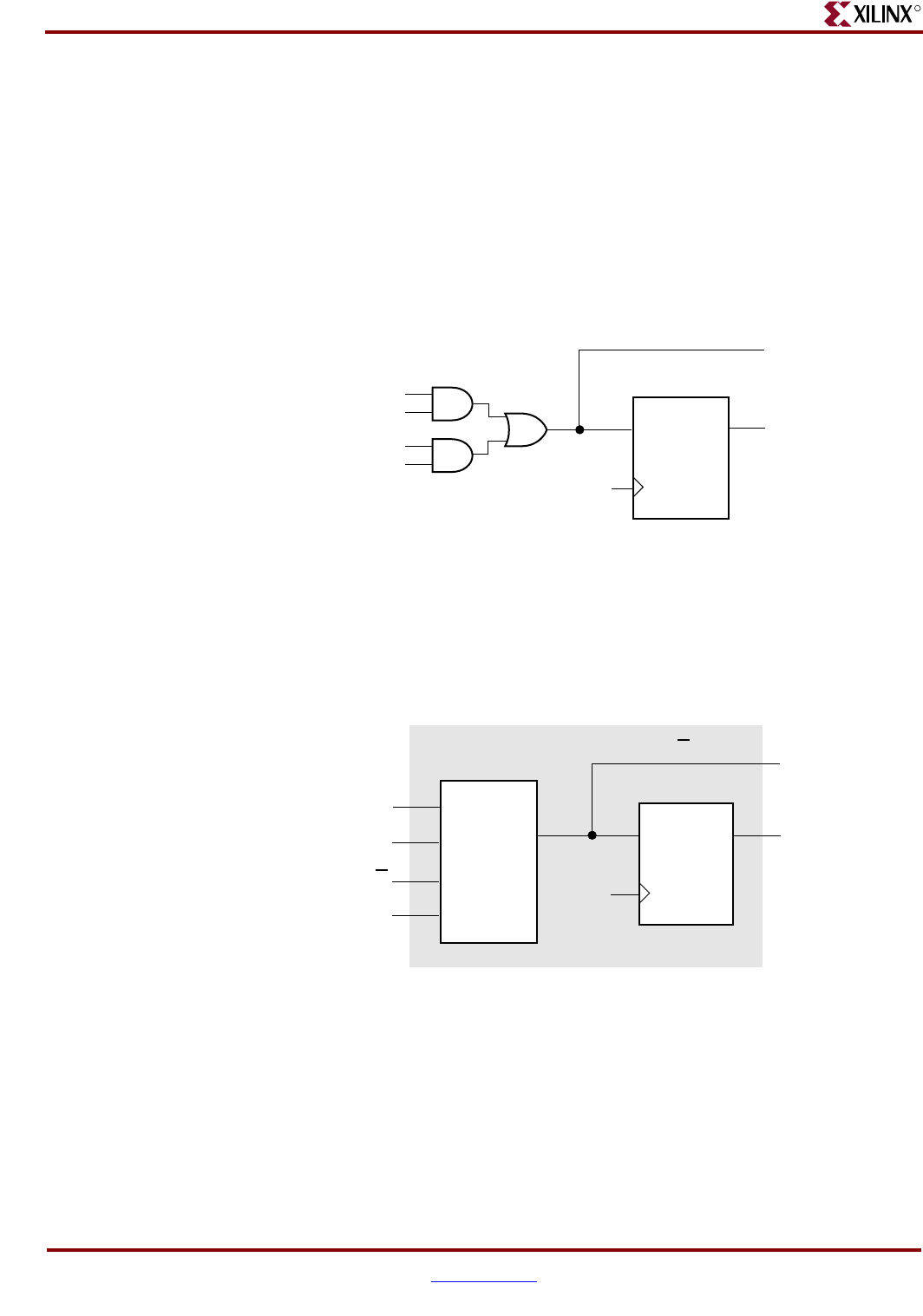

For example, consider the following logical circuit generated by NGDBuild from a design

file, shown in the following figure.

Observe the Boolean output from the combinatorial logic. Suppose that after running MAP

for the preceding circuit, you obtain the following result.

Observe that MAP has generated an active low (C) instead of an active high (C).

Consequently, the Boolean output for the combinatorial logic is incorrect. When you run

NetGen using the mapped.ngm file, you cannot detect the logical error because the delays

are back-annotated to the correct logical design, and not to the physical design.

Figure 7-4: Logical Circuit Representation

Figure 7-5: CLB Configuration

D

Q

CLK

A

*

B + C

*

D

A

B

C

D

X8549

D

Q

CLK

LUT

CLB

A

*

B + C

*

D

A

B

C

D

X8550