Development System Reference Guide www.xilinx.com 225

TRACE Reports

R

The tilde (~) also means that the path may exceed the numerical value listed next to the

tilde by as much as 20%. You can use the PENALIZE TILDE constraint to penalize

these delays by a specified percentage (see the Constraints Guide for a description of the

PENALIZE TILDE constraint).

• In a timing report, an “e” preceding a delay value shows that the delay value is

estimated because the path is not routed.

• TRACE detects when a path cycles (that is, when the path passes through a driving

output more than once), and reports the total number of cycles detected in the design.

When TRACE detects a cycle, it disables the cycle from being analyzed. If the cycle

itself is made up of many possible routes, each route is disabled for all paths that

converge through the cycle in question and the total number is included in the

reported cycle tally.

A path is considered to cycle outside of the influence of other paths in the design.

Thus, if a valid path follows a cycle from another path, but actually converges at an

input and not a driving output, the path is not disabled and contains the elements of

the cycle, which may be disabled on another path.

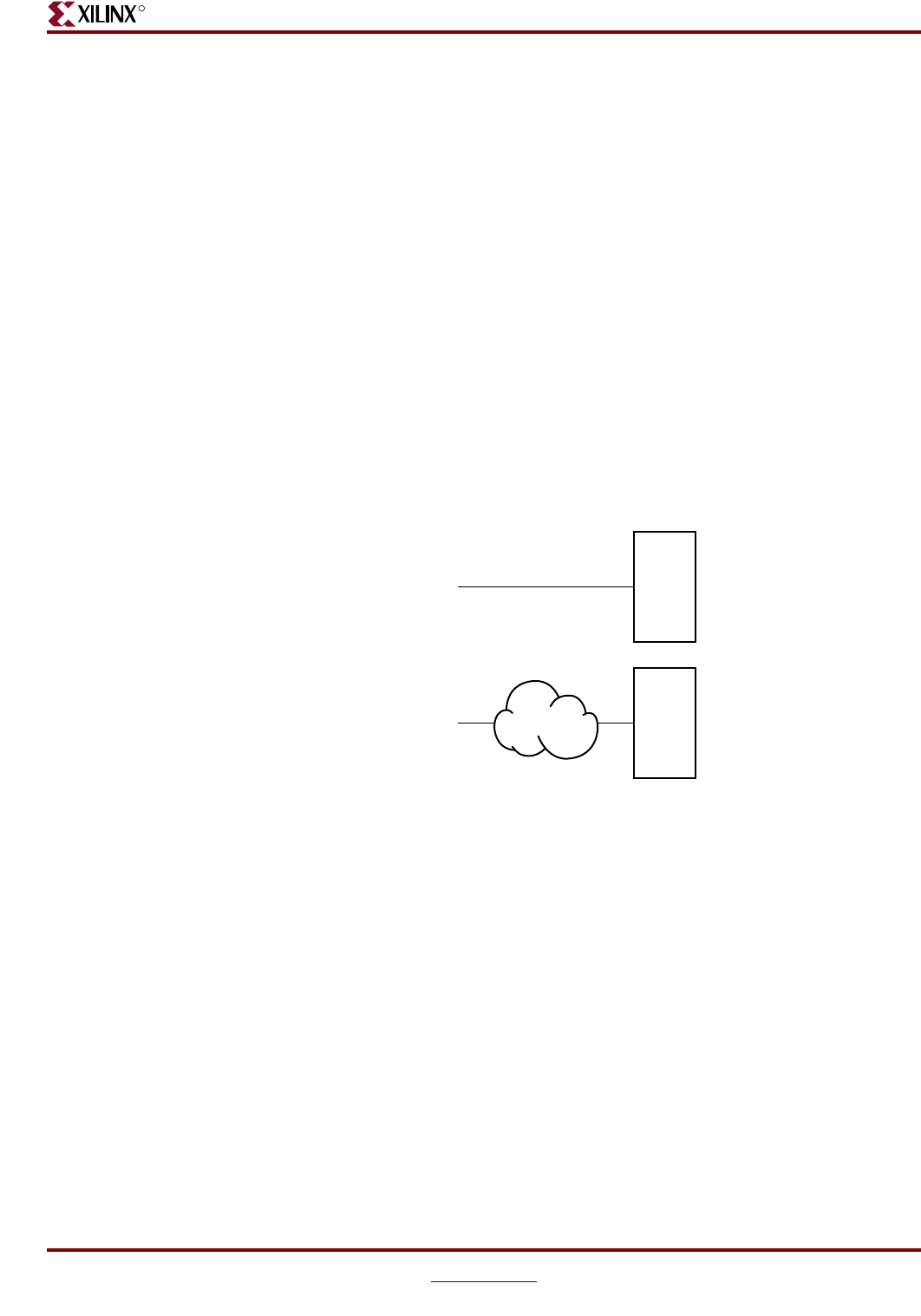

• Error counts reflect the number of path endpoints (register setup inputs, output pads)

that fail to meet timing constraints, not the number of paths that fail the specification,

as shown in the following figure.

If an error is generated at the endpoints of A and B, the timing report would lists two

errors—one for each endpoint.

• In Virtex-II designs, the MAP program places information that identifies dedicated

clocks in the PCF. You must use a physical constraints file (PCF) generated by the

MAP program to ensure accurate timing analysis on these designs.

Figure 12-5: Error reporting for failed timing constraints

X8630

9 paths

A

1 path

B