Development System Reference Guide www.xilinx.com 357

XFLOW Flow Types

R

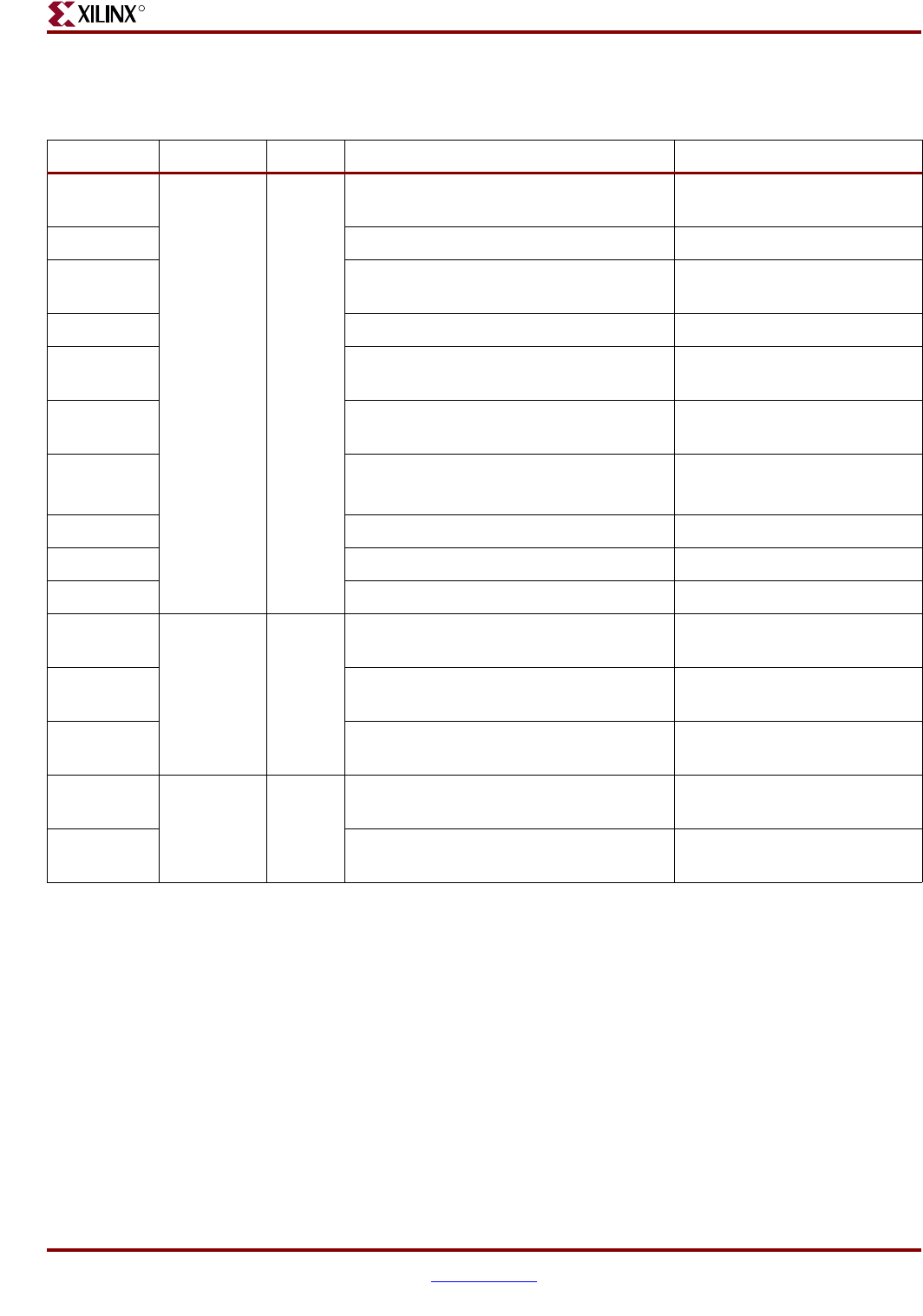

The following table lists the flow files invoked for each flow type.

Flow File Format

The flow file is an ASCII file that contains the following information:

Note:

You can use variables for the file names listed on the Input, Triggers, Export, and Report

lines. For example, if you specify

Input: <design>.vhd on the Input line, XFLOW automatically

reads the VHDL file in your working directory as the input file.

• ExportDir

This section specifies the directory in which to copy the output files of the programs in

the flow. The default directory is your working directory.

Note:

You can also specify the export directory using the –ed command line option. The

command line option overrides the ExportDir specified in the flow file.

Table 23-14: Xilinx Flow Files

Flow Type Flow File Devices Flow Phase Programs Run

–synth fpga.flw FPGA Synthesis XST, Synplicity,

Leonardo Spectrum

–initial Modular Design Initial Budgeting Phase NGDBuild

–module Modular Design Active Module

Implementation Phase

NGDBuild, MAP, PAR

–assemble Modular Design Final Assembly Phase NGDBuild, MAP, PAR

–implement Implementation NGDBuild, MAP, PAR,

TRACE

–mppr Implementation (with Multi-Pass Place

and Route)

NGDBuild, MAP, PAR

(multiple passes), TRACE

–tsim Timing

Simulation

NGDBuild, NetGen

–ecn Equivalence Checking NGDBuild, NetGen

–sta Static Timing Analysis NGDBuild, NetGen

–config Configuration BitGen

–synth cpld.flw CPLD Synthesis XST, Synplicity,

Leonardo Spectrum

–fit Fit NGDBuild, CPLDfit,

TAEngine, HPREP6

–tsim Timing

Simulation

TSim, NetGen

–synth fsim.flw FPGA/

CPLD

Synthesis XST, Synplicity,

Leonardo Spectrum

–fsim Functional

Simulation

NGDBuild, NetGen