Development System Reference Guide www.xilinx.com 349

XFLOW Flow Types

R

Xilinx provides the following option files for use with this flow type.

–fit (Fit a CPLD)

–fit option_file

This flow type incorporates logic from your design into physical macrocell locations in a

CPLD. It invokes the cpld.flw flow file and runs NGDBuild and CPLDfit to create a JED

file.

Xilinx provides the following option files for use with this flow type. These files allow you

to optimize your design based on different parameters.

The following example shows how to use a combination of flow types to fit a design and

generate a VHDL timing simulation netlist for a CPLD.

xflow -p xc2c64-4-cp56 -fit balanced.opt

-tsim generic_vhdl.opt main_pcb.edn

–fsim (Create a File for Functional Simulation)

–fsim option_file

Note:

The –fsim flow type can be used alone or with the –synth flow type. It cannot be combined

with the –implement, –tsim, –fit, or –config flow types.

This flow type generates a file that can be used for functional simulation of an FPGA or

CPLD design. It invokes the fsim.flw flow file and runs NGDBuild and NetGen to create a

func_sim.edn, func_sim.v, or func_sim.vhdl file. This file contains a netlist description of

your design in terms of Xilinx simulation primitives. You can use the functional simulation

file to perform a back-end simulation with a simulator.

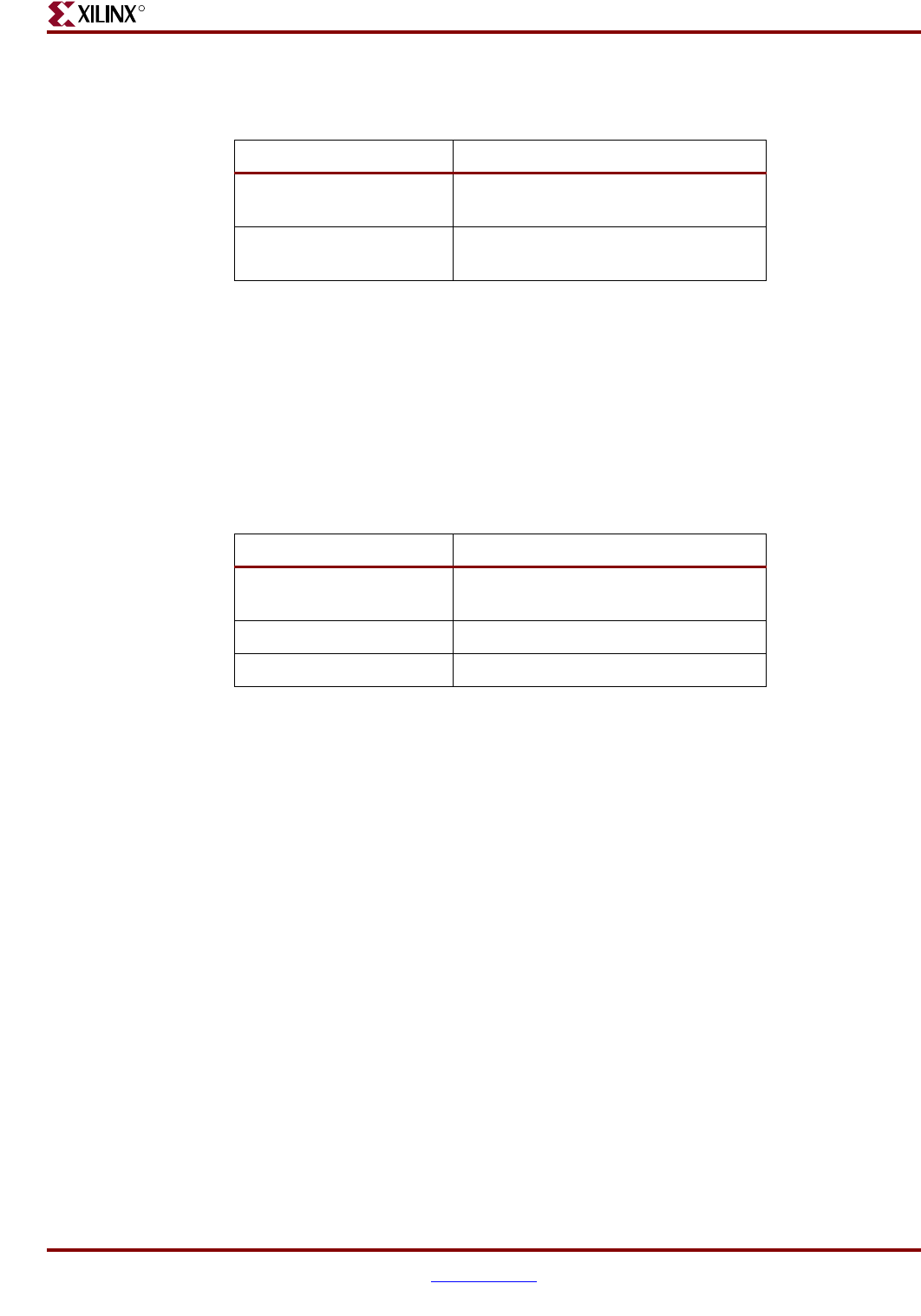

Table 23-5: Option Files for –ecn Flow Type

Option Files Description

conformal_verilog.opt Option file for equivalence checking

for conformal

formality_verilog.opt Option file for equivalence checking

for formality

Table 23-6: Option Files for –fit Flow Type

Option Files Description

balanced.opt Optimized for a balance between

speed and density

speed.opt Optimized for speed

density.opt Optimized for density