348 www.xilinx.com Development System Reference Guide

Chapter 23: XFLOW

R

Xilinx provides the following option files for use with this flow type. These files allow you

to optimize your design based on different parameters.

The following example shows how to assemble a Modular Design with a top-level design

named “top”:

xflow –p xc2v250fg256-5 –assemble balanced.opt

–pd ../pims top.ngo

–config (Create a BIT File for FPGAs)

–config option_file

This flow type creates a bitstream for FPGA device configuration using a routed design. It

invokes the fpga.flw flow file and runs the BitGen program.

Xilinx provides the bitgen.opt option file for use with this flow type.

To use a netlist file as input, you must use the –implement flow type with the –config flow

type. The following example shows how to use multiple flow types to implement and

configure an FPGA:

xflow –p xc2v250fg256-5 –implement balanced.opt

–config bitgen.opt testclk.edf

To use this flow type without the –implement flow type, you must use a placed and routed

NCD file as input.

–ecn (Create a File for Equivalence Checking)

–ecn option_file

This flow type generates a file that can be used for formal verification of an FPGA design.

It invokes the fpga.flw flow file and runs NGDBuild and NetGen to create a netgen.ecn file.

This file contains a Verilog netlist description of your design for equivalence checking.

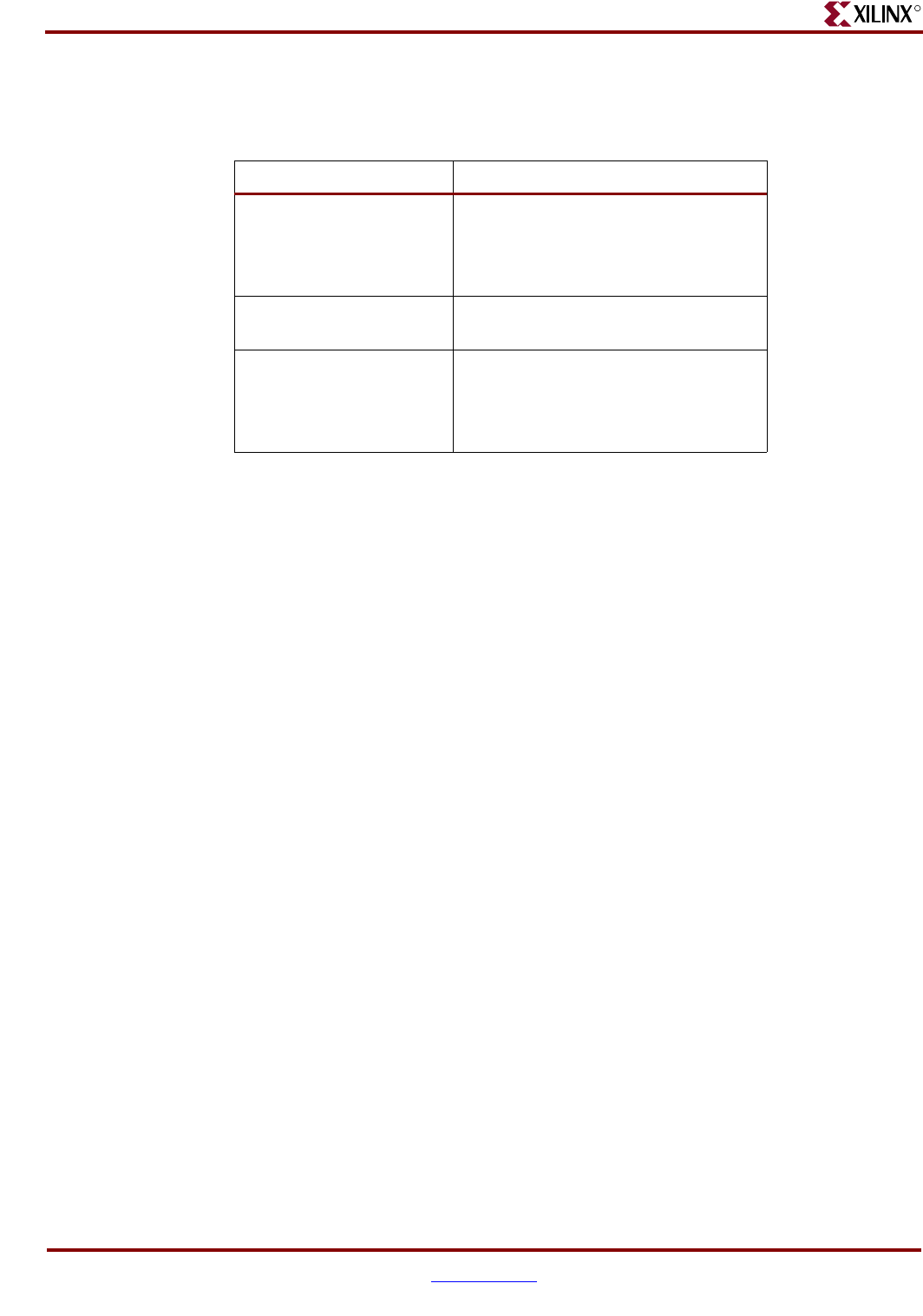

Table 23-4: Option Files for –assemble Flow Type

Option Files Description

fast_runtime.opt Optimized for fastest runtimes at the

expense of design performance

Recommended for medium to slow

speed designs

balanced.opt Optimized for a balance between

speed and high effort

high_effort.opt Optimized for high effort at the

expense of longer runtimes

Recommended for creating designs

that operate at high speeds