356 www.xilinx.com Development System Reference Guide

Chapter 23: XFLOW

R

Xilinx provides the following option files, which are targeted to specific vendors, for use

with this flow type.

The following example shows how to use a combination of flow types to fit and perform a

VHDL timing simulation on a CPLD:

xflow -p xc2c64-4-cp56 -fit balanced.opt -tsim generic_vhdl.opt

main_pcb.vhd

Flow Files

When you specify a flow type on the command line, XFLOW invokes the appropriate flow

file and executes some or all of the programs listed in the flow file. These files have a .flw

extension. Programs are run in the order specified in the flow file.

Xilinx provides three flow files. You can edit these flow files, to add a new program,

modify the default settings, and add your own commands between Xilinx programs.

However, you cannot create new flow files of your own.

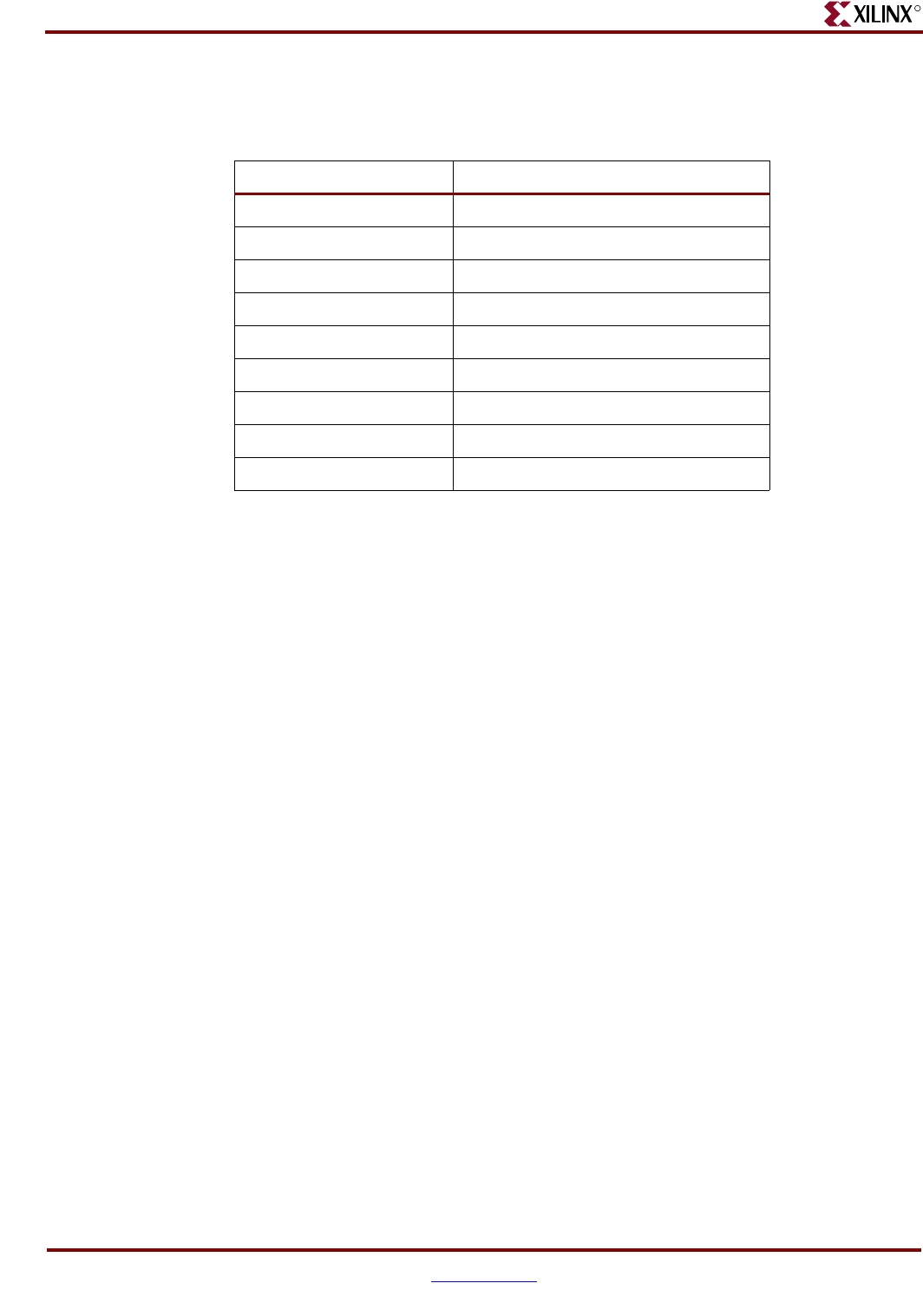

Table 23-13: Option Files for –tsim Flow Type

Option File Description

generic_vhdl.opt Generic VHDL

modelsim_vhdl.opt Modelsim VHDL

generic_verilog.opt Generic Verilog

modelsim_verilog.opt Modelsim Verilog

scirocco_vhdl.opt Scirocco VHDL

nc_verilog.opt NC Verilog

verilog_xl.opt Verilog-XL

vcs_verilog.opt VCS Verilog

nc_vhdl.opt NC VHDL