38 www.xilinx.com Development System Reference Guide

Chapter 2: Design Flow

R

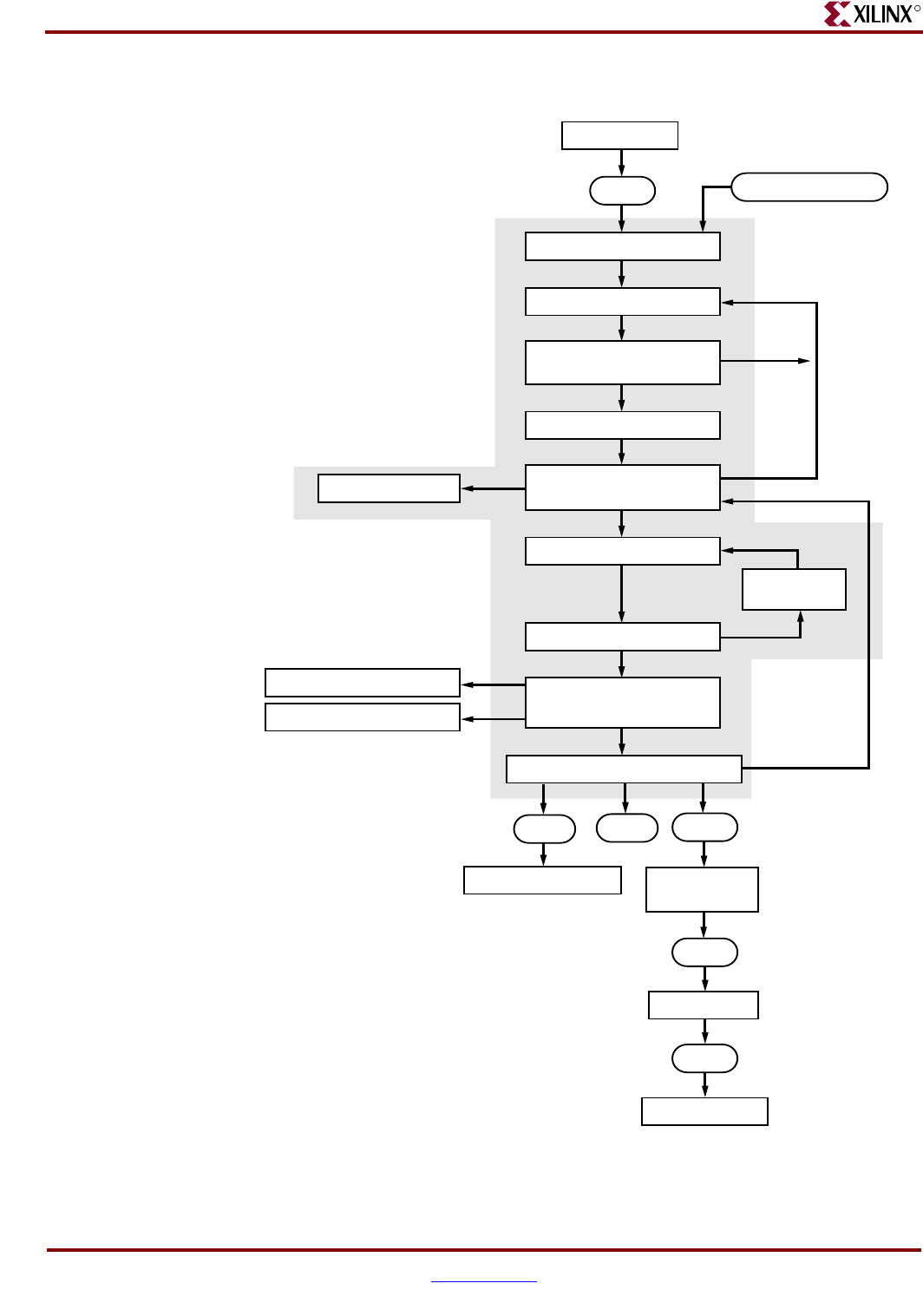

The following figure shows the design implementation process for CPLD designs:

Figure 2-6: Design Implementation Flow (CPLDs)

X9493

Design Loader

NGDBuild

NGD

Auto Device/Speed Selector

Logic Synthesis

Technology Mapping

Global Net Optimization

Logic Optimization

Partitioning

Exporting

Assignments

Export Level Generator

PTerm Mapping

Power/Slew Optimization

Post-Mapping

Enhancements

Routing

CPLD Fitter

Implementation Options

RPT

GYD

Pin Feedback Generation

Fitter Report (Text)

JED

HPLUSAS6

HPREP6

iMPACT

VM6

VM6