Development System Reference Guide www.xilinx.com 355

XFLOW Flow Types

R

If you have multiple VHDL files, you must list all the source files in a text file, one per line

and pass that information to XFLOW using the –g (Specify a Global Variable) option.

Assume that the file that lists all source files is filelist.txt and design_name.vhd

is the top level design. Use the following example:

xflow -p xc2v250fg256-5 -g srclist:filelist.txt -synth

synplicity_vhdl.opt design_name.vhd

The same rule applies for Verilog too.

The following example shows how to use a combination of flow types to synthesize and

implement a design:

xflow -p xc2v250fg256-5 -synth xst_vhdl.opt -implement balanced.opt

testclk.prj

Option Files for -synth Flow Types

Xilinx provides the following option files for use with the –synth flow type. These files

allow you to optimize your design based on different parameters.

The following example shows how to use a combination of flow types to synthesize and

implement a design:

xflow –p xc2v250fg256-5 –synth xst_vhdl.opt -implement balanced.opt

testclk.prj

–tsim (Create a File for Timing Simulation)

–tsim option_file

This flow type generates a file that can be used for timing simulation of an FPGA or CPLD

design. It invokes the fpga.flw or cpld.flw flow file, depending on your target device. For

FPGAs, it runs NetGen. For CPLDs, it runs TSim and NetGen. This creates a time_sim.v or

time_sim.vhdl file that contains a netlist description of your design in terms of Xilinx

simulation primitives. You can use the output timing simulation file to perform a back-end

simulation with a simulator.

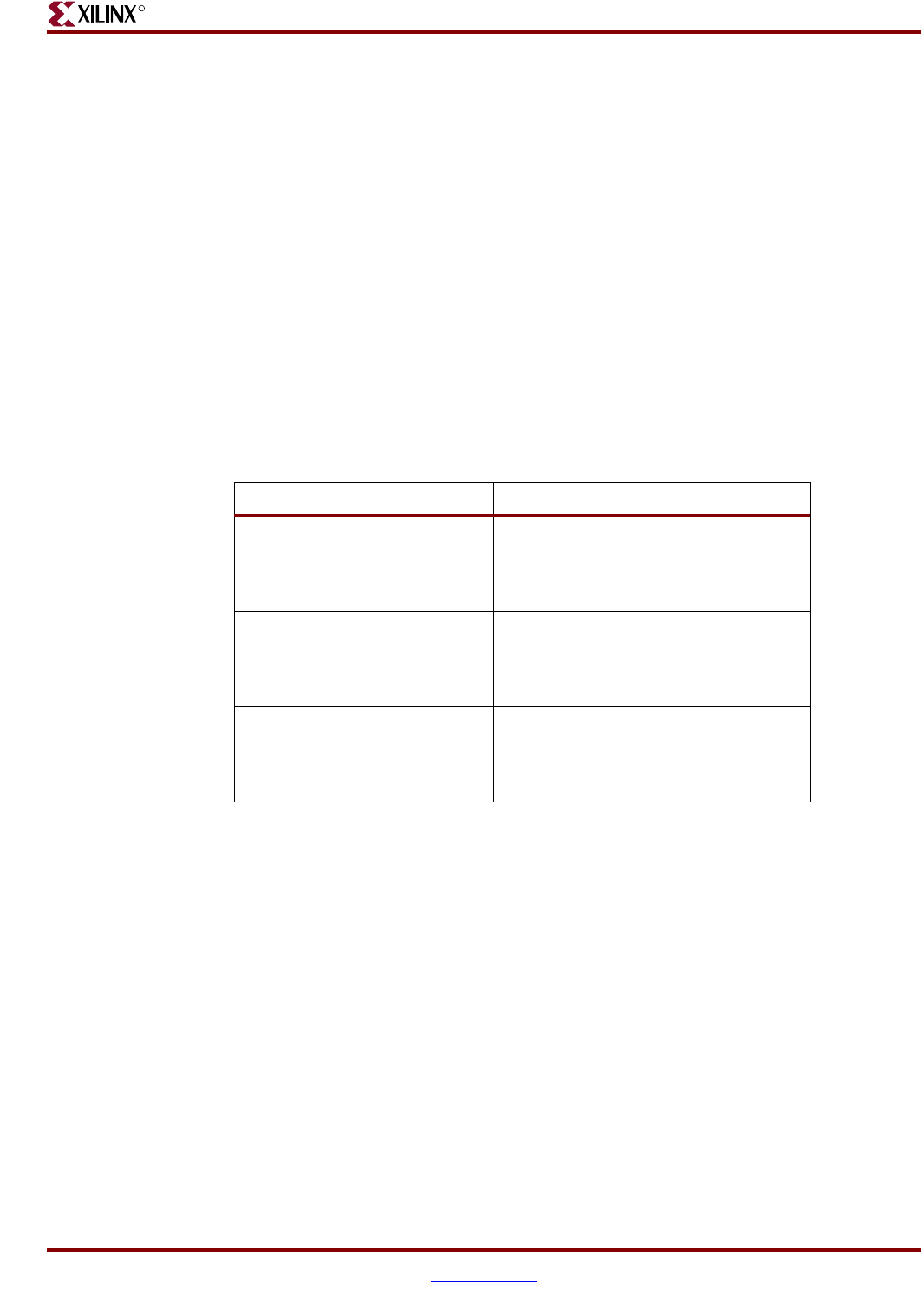

Table 23-12: Option Files for –synth Flow Type

Option File Description

xst_vhdl.opt

leonardospectrum_vhdl.opt

synplicity_vhdl.opt

Optimizes a VHDL source file for

speed, which reduces the number of

logic levels and increases the speed of

the design

xst_verilog.opt

leonardospectrum_verilog.opt

synplicity_verilog.opt

Optimizes a Verilog source file for

speed, which reduces the number of

logic levels and increases the speed of

the design

xst_mixed.opt Optimizes a mixed level VHDL and

Verilog source file for speed, which

reduces the number of logic levels and

increases the speed of the design.