Development System Reference Guide www.xilinx.com 41

Design Verification

R

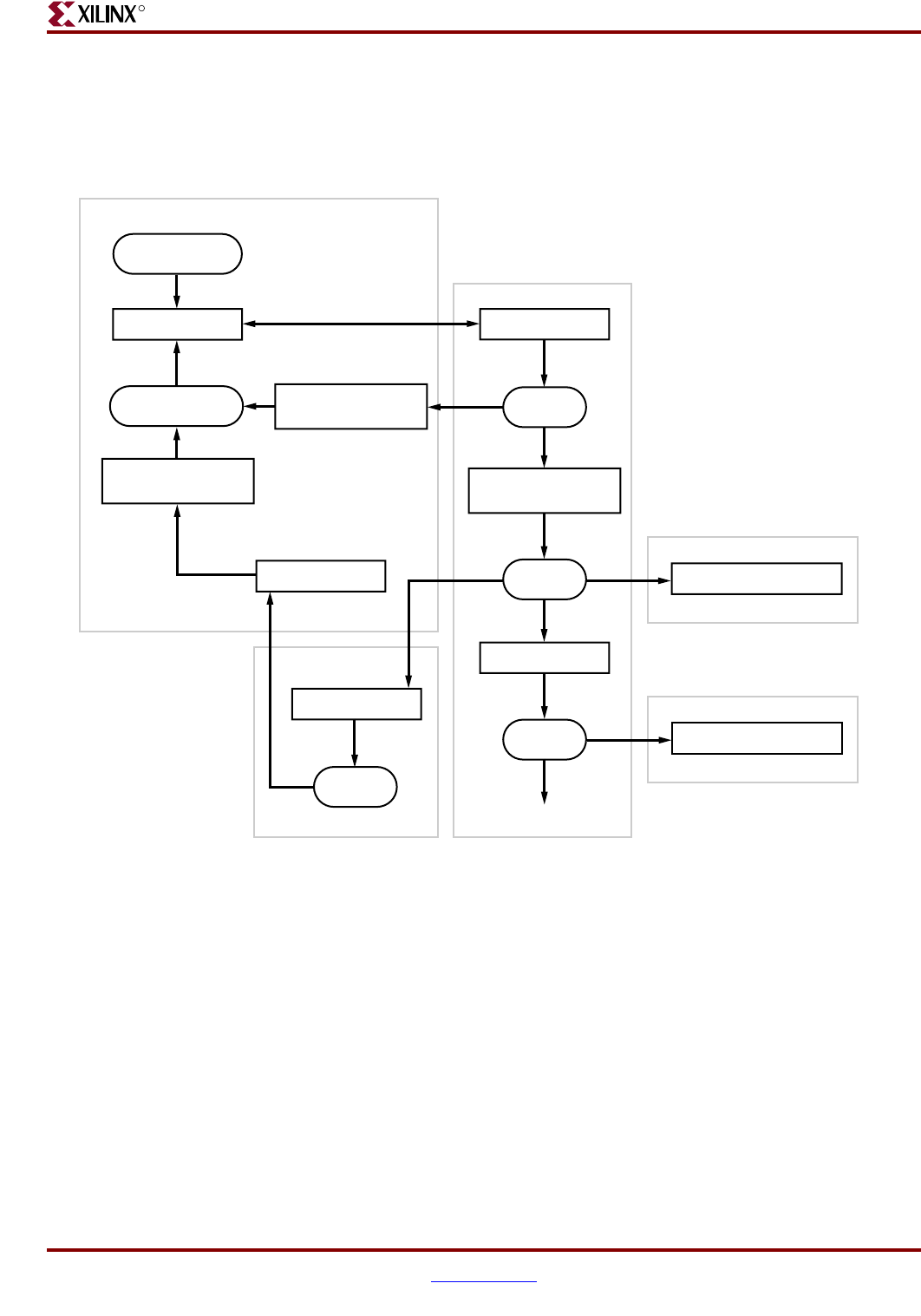

Design verification procedures should occur throughout your design process, as shown in

the following figures.

Figure 2-7: Three Verification Methods of the Design Flow (FPGAs)

X9556

Static Timing Analysis

Input Stimulus

Simulation Netlist

Simulation

Xilinx FPGA

Design Entry

Integrated Tool

Functional Simulator

Paths

Timing Simulation Path

Simulation

Static Timing

In-Circuit Verification

In-Circuit Verification

Basic Design Flow

NGD

NCD

BitGen

BIT

Mapping, Placement

and Routing

Translate to

Simulator Format

Translate to

Simulator Format

Back-Annotation

NGA

Translation