Development System Reference Guide www.xilinx.com 337

Preserving and Writing Hierarchy Files

R

–sta (Generate Static Timing Analysis Netlist)

The –sta option writes a static timing analysis netlist.

–tm (Top Module Name)

–tm top_module_name

By default (without the –tm option), the output files inherit the top module name from the

input NCD file. The –tm option changes the name of the top-level module name appearing

within the NetGen output files.

–w (Overwrite Existing Files)

The –w option causes NetGen to overwrite the .v file if it exists. By default, NetGen does

not overwrite the netlist file.

All other output files are automatically overwritten.

Preserving and Writing Hierarchy Files

When hierarchy is preserved during synthesis and implementation using the

KEEP_HIERARCHY constraint, the NetGen –mhf option writes separate netlists and SDF

files (if applicable) for each piece of hierarchy.

The hierarchy of STARTUP and glbl (Verilog only) modules is preserved in the output

netlist. If the -mhf option is used and there is at least one hierarchical block with the

KEEP_HIERARCHY constraint in the design, NetGen writes out a separate netlist file for

the STARTUP and glbl modules. If there is no block with the KEEP_HIERARCHY

constraint, the -mhf option is ignored even if there are STARTUP and glbl modules in the

design.

This section describes the output file types produced with the –mhf option. The type of

netlist output by NetGen, depends on whether you are running the NetGen simulation,

equivalence checking, or static timing analysis flow. For simulation, NetGen outputs a

Verilog or VHDL file. The –ofmt option must be used to specify the output file type you

wish to produce when you are running the NetGen simulation flow.

Note:

When Verilog is specified, the $sdf_annotate is included in the Verilog netlist for each module.

The following table lists the base naming convention for hierarchy output files:

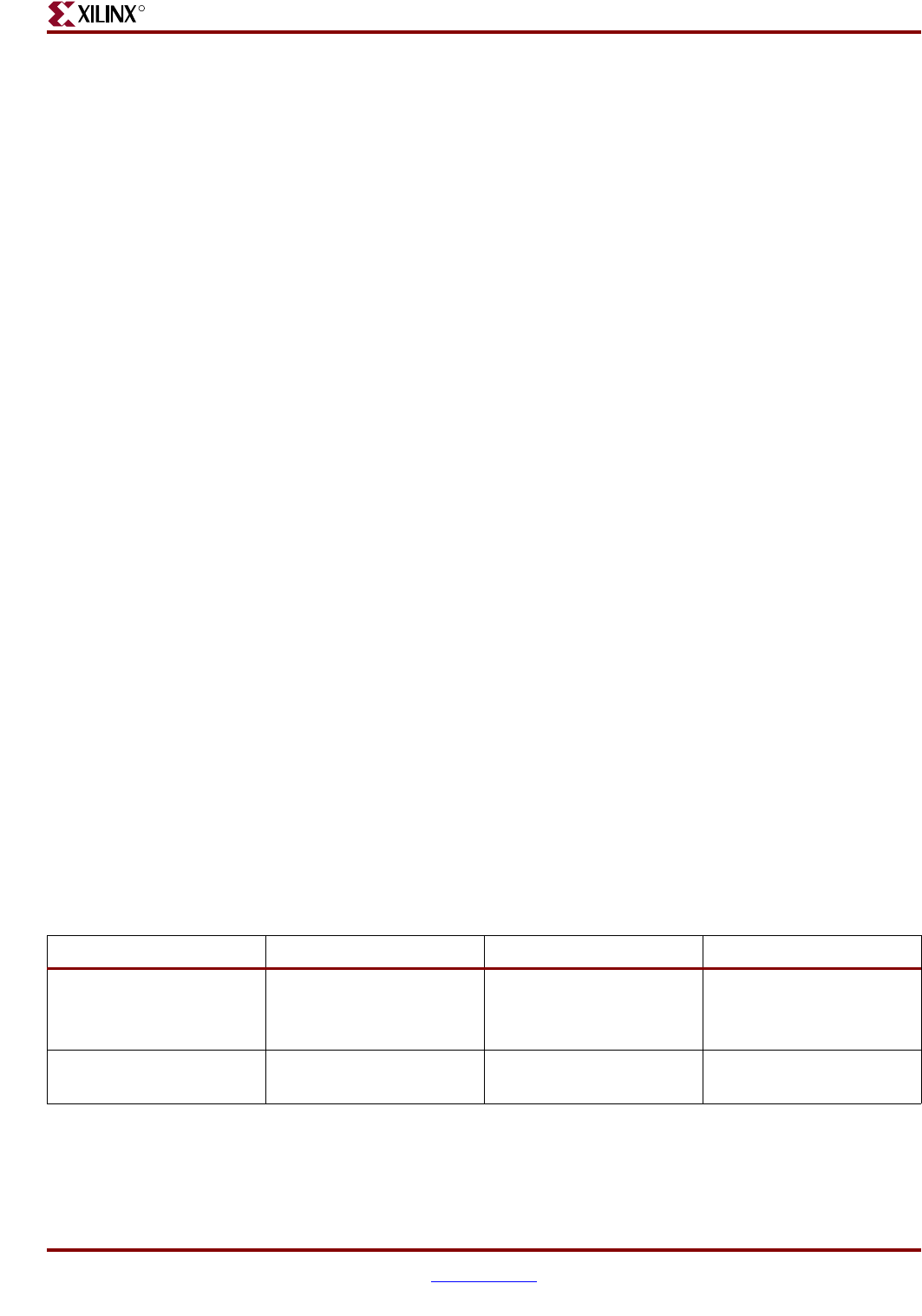

Table 22-2: Hierarchy File Content

Hierarchy File Content Simulation Equivalence Checking Static Timing Analysis

File with Top-level

Module

[input_filename] (default),

or user specified output

filename

[input_filename].ecn, or

user specified output

filename

[input_filename].sta, or

user specified output

filename

File with Lower Level

Module

[module_name].sim [module_name].ecn [module_name].sta