Development System Reference Guide www.xilinx.com 221

TRACE Reports

R

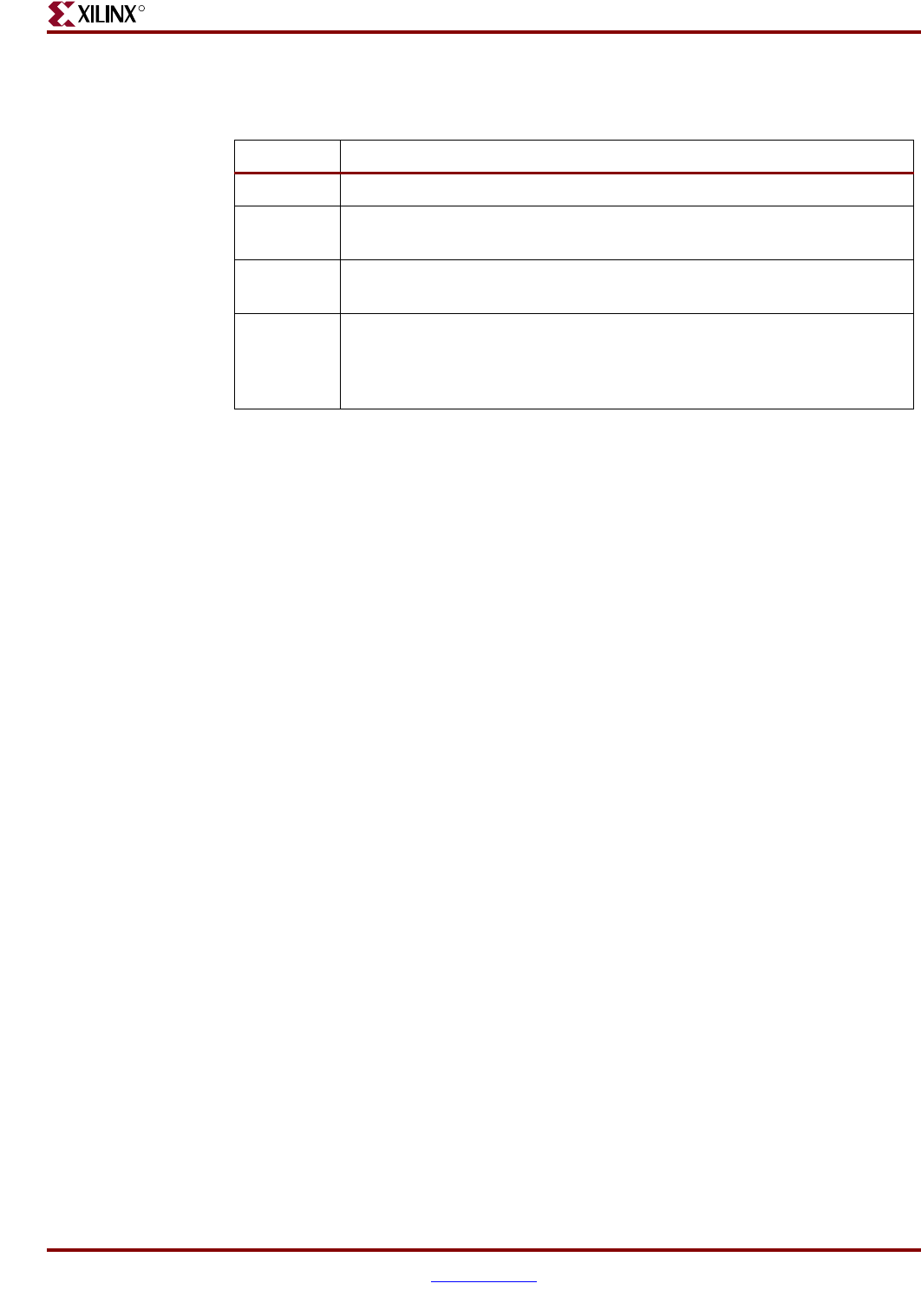

The following table lists the terminology for path delay constraints:

Paths showing delays that do not meet this condition generate timing errors in the timing

report.

Clock Skew and Setup Checking

Clock skew must be accounted for in register-to-register setup checks. For register-to-

register paths, the data delay must reach the destination register within a single clock

period. The timing analysis software ensures that any clock skew between the source and

destination registers is accounted for in this check.

Note:

Clock skew must be accounted for in register-to-register setup checks. For register-to-

register paths, the data delay must reach the destination register within a single clock period. The

timing analysis software ensures that any clock skew between the source and destination registers is

accounted for in this check. By default, the clock skew of all non-dedicated clocks, local clocks, and

dedicated clocks is analyzed.

A setup check performed on register-to-register paths checks the following condition:

Slack = constraint + Tsk - (Tpath + Tsu)

The following table lists the terminology for clock skew and setup checking:

Table 12-1: Path Delay Constraint Terminology

Term Definition

logicdelay Pin-to-pin delay through a component.

routedelay Signal delay between component pins in a path. This is an estimated

delay if the design is placed but not routed.

setuptime For clocked paths only, the time that data must be present on an input pin

before the arrival of the triggering edge of a clock signal.

clockskew For register-to-register clocked paths only, the difference between the

amount of time the clock signal takes to reach the destination register and

the amount of time the clock signal takes to reach the source register.

Clock skew is discussed in the following section.