318 www.xilinx.com Development System Reference Guide

Chapter 22: NetGen

R

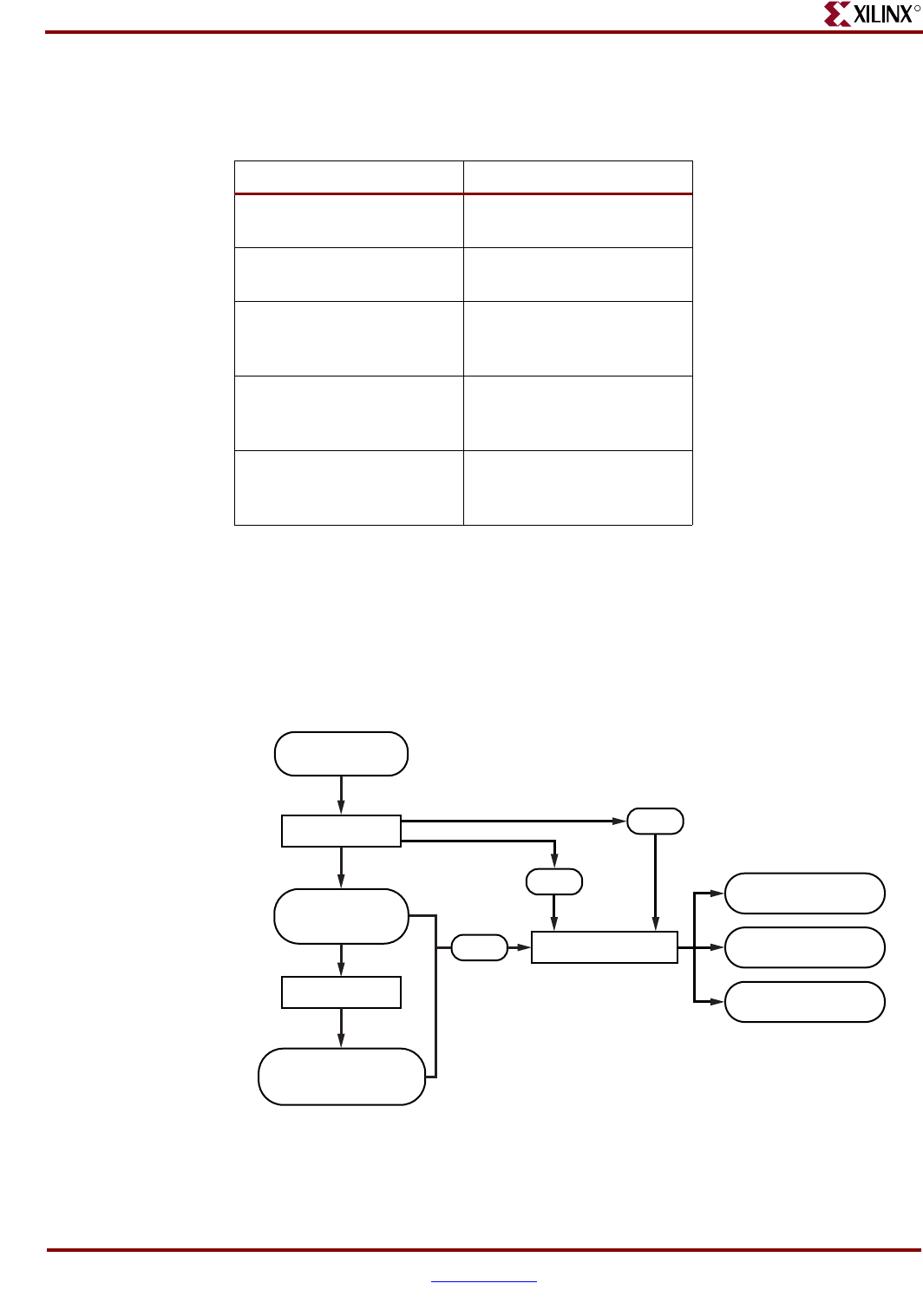

The flow type that NetGen runs is based on the input design file (NGC, NGD, or NCD).

The following table shows the output file types, based on the input design files:

NetGen can take an implemented design file and write out a single netlist for the entire

design, or multiple netlists for each module of a hierarchical design. Individual modules of

a design can be simulated on their own, or together at the top-level. Modules identified

with the KEEP_HIERARCHY attribute are written as user-specified Verilog, VHDL, and

SDF netlists with the “–mhf (Multiple Hierarchical Files)”option. See “Preserving and

Writing Hierarchy Files” for additional information.

The following figure outlines the NetGen flow for implemented FPGA designs.

Figure 22-1: NetGen Flow

Table 22-1: NetGen Output File Types

Input Design File Output File Type

NGC UNISIM-based functional

simulation netlist

NGD SIMPRIM-based functional

netlist

NCA from CPLD SIMPRIM-based netlist,

along with a full timing

SDF file.

NCD from MAP SIMPRIM-based netlist,

along with a partial timing

SDF file

NCD from PAR SIMPRIM-based netlist,

along with a full timing

SDF file

X9980

PAR

NetGen

MAP

NGD

Logical Design

NCD

Physical Design

(Mapped)

NCD

Physical Design

(Placed and Routed)

NGM

Simulation Netlist

Equivalence Checking

Netlist

Static Timing Analysis

Netlist

PCF

NCD