52 www.xilinx.com Development System Reference Guide

Chapter 2: Design Flow

R

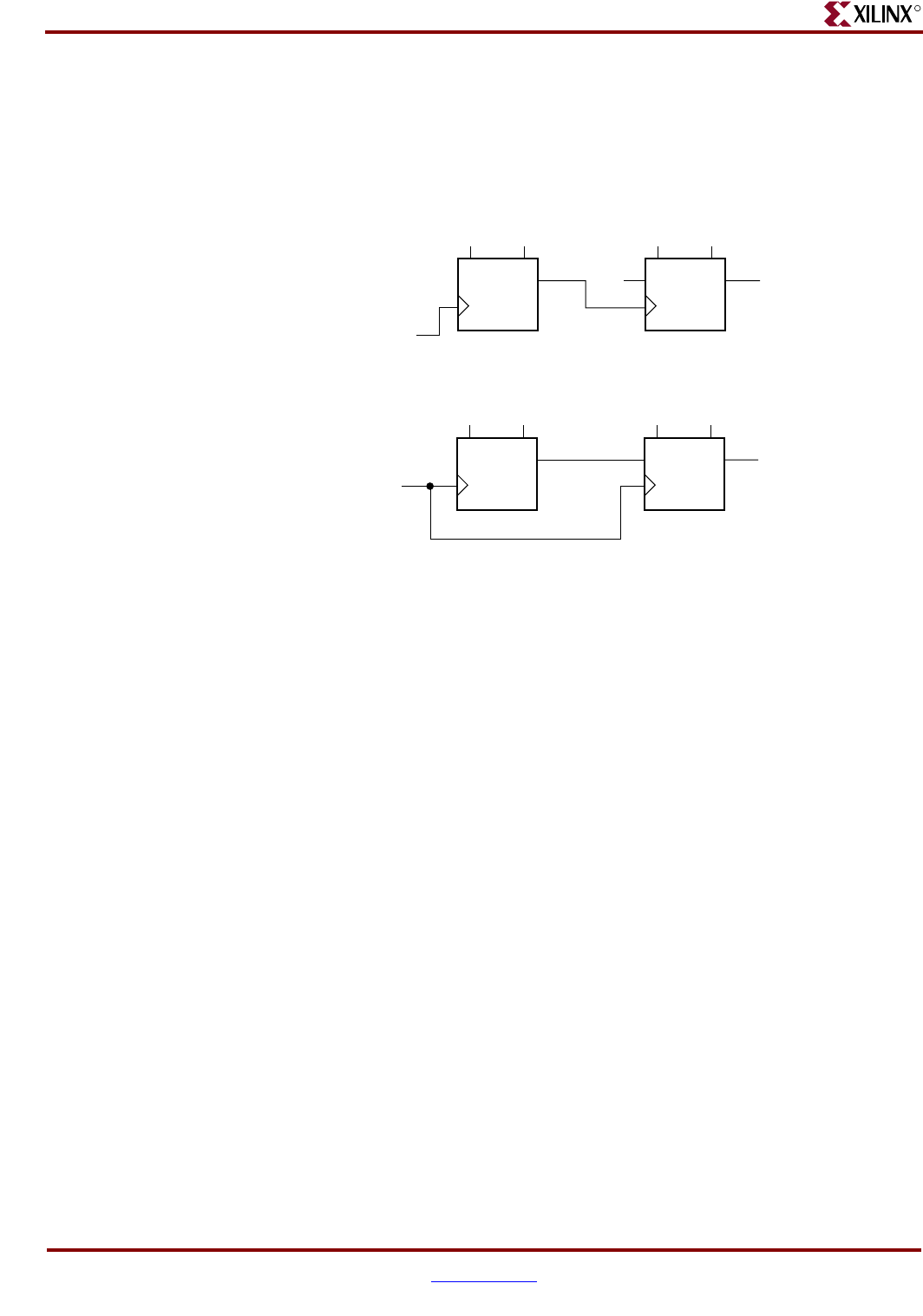

The following figure shows how you can create a synchronous design using the CE input.

In this case, the TC of the first stage is connected directly to the CE of the second stage.

Other Synchronous Design Considerations

Other considerations for achieving a synchronous design include the following:

• Use clock enables instead of gated clocks to control the latching of data into registers.

• If your design has more clocks than the number of global clock distribution networks,

try to redesign to reduce the number of clocks. Otherwise, put the clocks that have the

lowest fanout onto normally routed nets, and specify a low MAXSKEW rating. A

clock net routed through a normal net has skew.

• Use the Virtex low skew resources. Make sure the MAXSKEW rating is not specified

when using these resources.

Figure 2-14: Two 8-Bit Counters Connected to Create a 16-Bit Counter

a) 16-bit counter with TC connected to the clock.

TC

Q

0

Q

7. . . .

TC

Q

8

Q

15. . . .

CE

X2093

TC

b) 16-bit counter with TC connected to the clock-enable.

Q

0

Q

7. . . .

TC

Q

8

Q

15. . . .

CE

CLK

IMPROPER METHOD