Development System Reference Guide www.xilinx.com 345

XFLOW Output Files

R

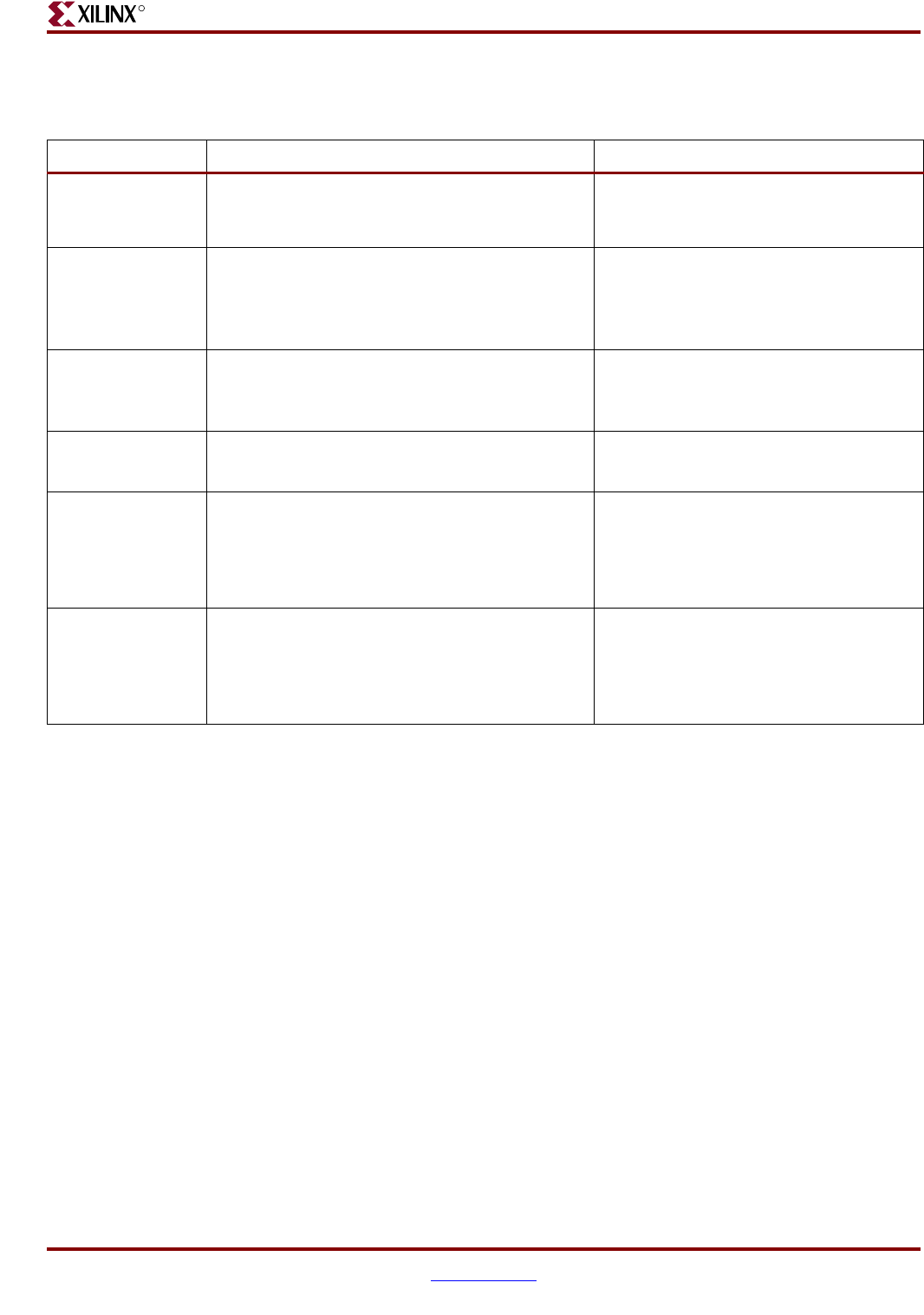

The following table lists files that can be generated for both FPGA and CPLD designs.

Table 23-1: XFLOW Output Files (FPGAs and CPLDs)

File Name Description To Generate this File...

design_name.bld This report file contains information about the

NGDBuild run, in which the input netlist is

translated to an NGD file.

Flow file must include “ngdbuild” (Use

the –implement or –fit flow type)

time_sim.sdf

func_sim.sdf

This Standard Delay Format file contains the

timing data for a design.

Flow file must include “netgen” (Use the

–tsim or –fsim flow type)

Input must be an NGA file, which

includes timing information

time_sim.tv

func_sim.tv

This is an optional Verilog test fixture file. Flow file must include “netgen” (Use the

–tsim or –fsim flow type)

time_sim.tvhd

func_sim.tvhd

This is an optional VHDL testbench file. Flow file must include “netgen” (Use the

–tsim or –fsim flow type)

time_sim.v

func_sim.v

This Verilog netlist is a

simulation netlist expressed in terms of Xilinx

simulation primitives. It differs from the Verilog

input netlist and should only be used for

simulation, not implementation.

Flow file must include “netgen” (Use the

–tsim or –fsim flow type)

time_sim.vhd

func_sim.vhd

This VHDL netlist is a simulation netlist

expressed in terms of Xilinx simulation

primitives. It differs from the VHDL input netlist

and should only be used for simulation, not

implementation.

Flow file must include “netgen” (Use the

–tsim or –fsim flow type)