32 www.xilinx.com Development System Reference Guide

Chapter 2: Design Flow

R

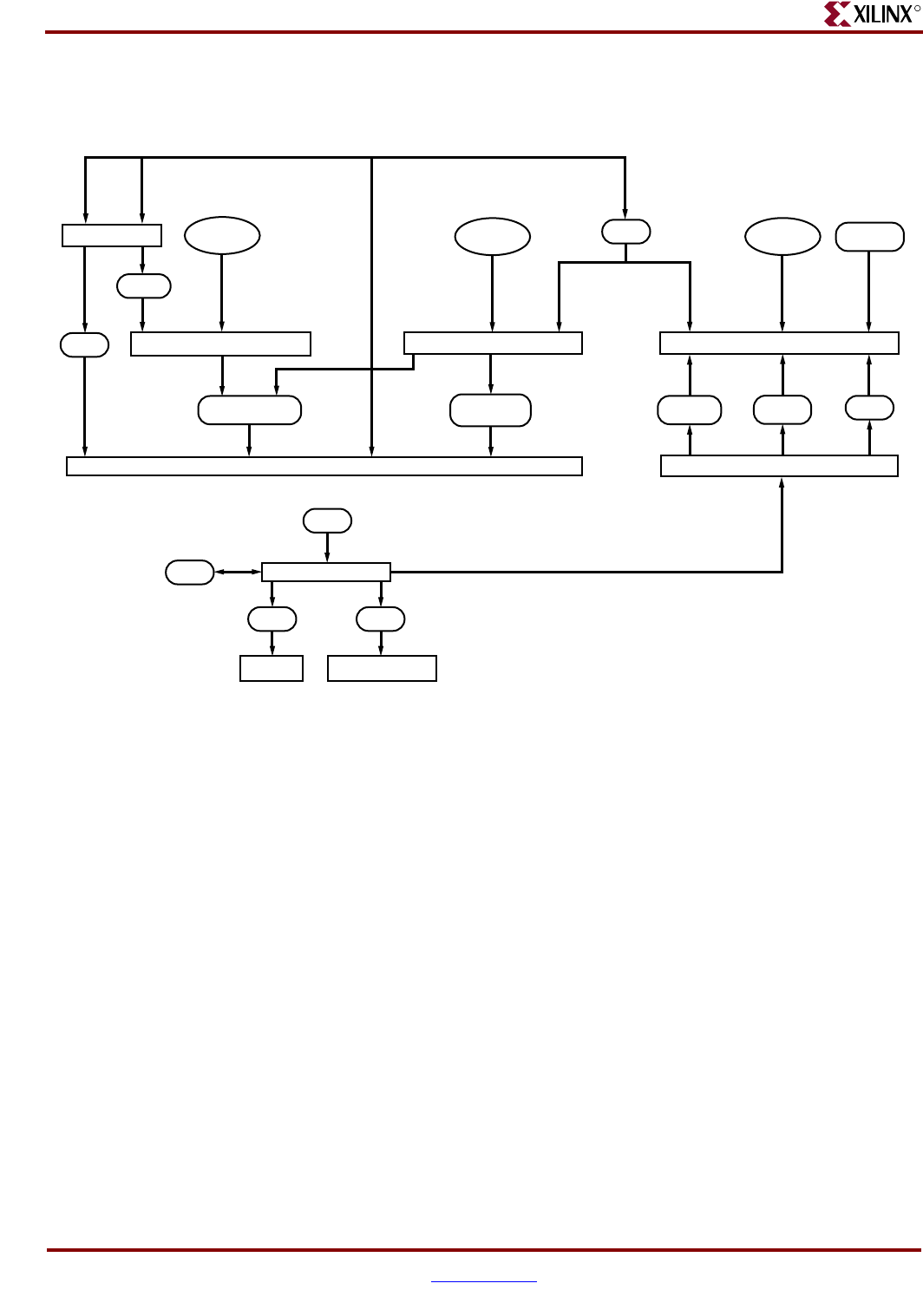

The following figure shows the Xilinx software flow chart for CPLD designs.

Figure 2-3: Xilinx Software Design Flow (CPLDs)

X10294

V &

SDF 2.1

VHD &

SDF 2.1

Simulation

Libraries

CORE Generator

Schematic Capture

NGD

HDL

Symbol

GYD

EDIF

2 0 0

CPLD Fitter

NGC

JED VM6

iMPACT Timing Analyzer

Synthesis Simulation

EDIF 2 0 0 &

Constraints/NCF

NGC

(XST Netlist)

NetGen

Testbench

Stimulus

NGDBuild NGDBuildNGDBuild

Synthesis

Libraries

Schematic

Libraries