322 www.xilinx.com Development System Reference Guide

Chapter 22: NetGen

R

Output files for FPGA Timing Simulation

• SDF file—This SDF 3.0 compliant standard delay format file contains delays obtained

from the input design files.

• V file—This is a IEEE 1364-2001 compliant Verilog HDL file that contains the netlist

information obtained from the input design files. This file is a simulation model of the

implemented design and cannot be synthesized or used in any manner other than

simulation.

• VHD file—This VHDL IEEE 1076.4 VITAL-2000 compliant VHDL file contains the

netlist information obtained from the input design files. This file is a simulation model

of the implemented design and cannot be synthesized or used in any other manner

than simulation.

CPLD Timing Simulation

You can use the NetGen Timing Simulation flow to verify the timing of a CPLD design

after it is implemented using CPLDfit and the delays are annotated using the –tsim option.

The input file is the annotated NGA file from the TSIM program.

Note:

See Chapter 18, “CPLDfit” and Chapter 19, “TSIM” for additional information.

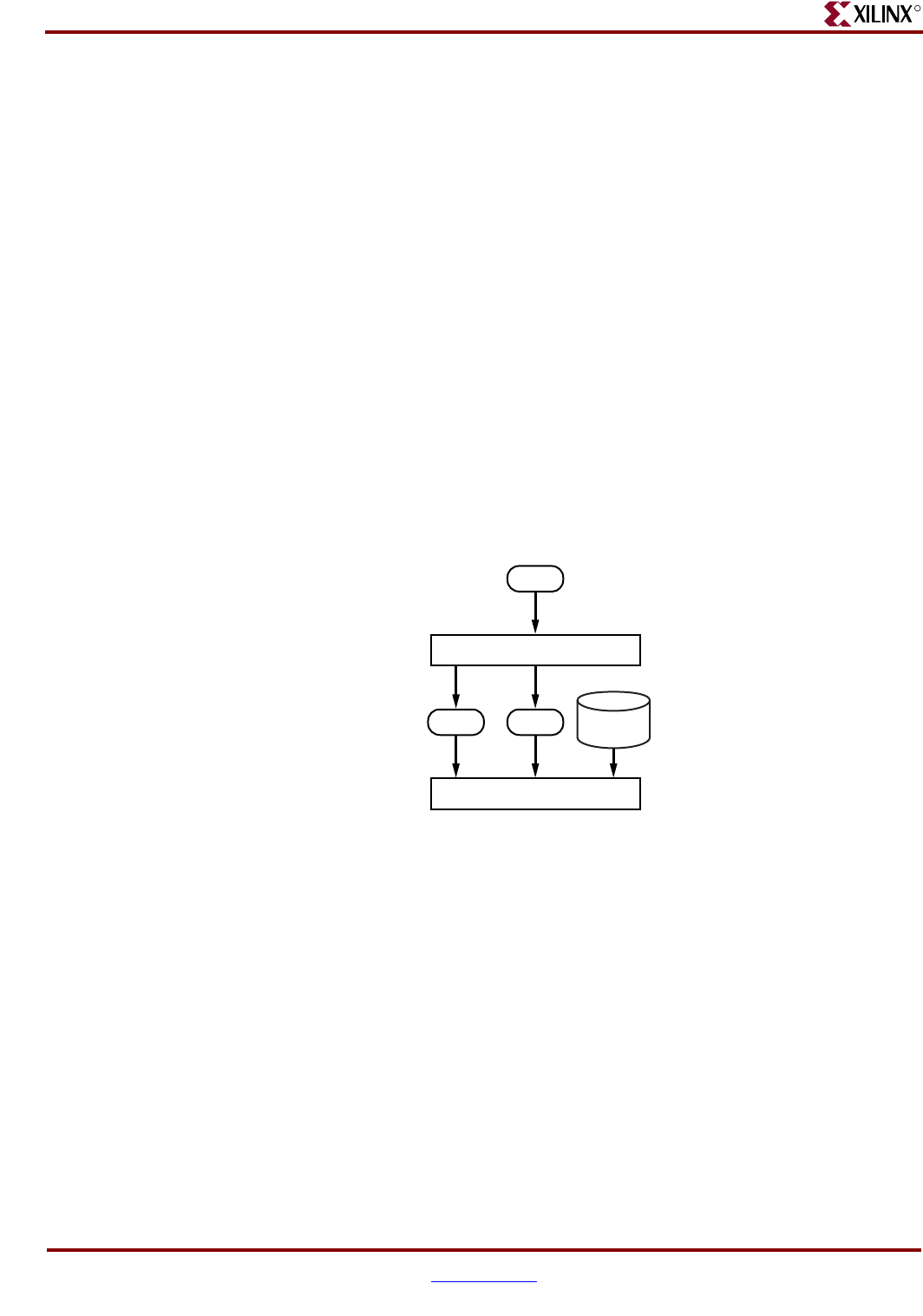

The figure below illustrates the NetGen Timing Simulation flow using a CPLD design.

Figure 22-3: CPLD Timing Simulation

Input files for CPLD Timing Simulation

The CPLD Timing Simulation flow uses the following files as input:

• NGA file—This native generic annotated file is a logical design file from TSIM that

contains Xilinx primitives. See Chapter 19, “TSIM” for additional information.

Output files for CPLD Timing Simulation

The NetGen Simulation Flow uses the following files as output:

• SDF file—This standard delay format file contains delays obtained from the input

NGA file.

X9982

NetGen

NGA

SDF

Simulation Tool

Simprim

Library

V/VHD