40 www.xilinx.com Development System Reference Guide

Chapter 2: Design Flow

R

Design Verification

Design verification is testing the functionality and performance of your design. You can

verify Xilinx designs in the following ways:

• Simulation (functional and timing)

• Static timing analysis

• In-circuit verification

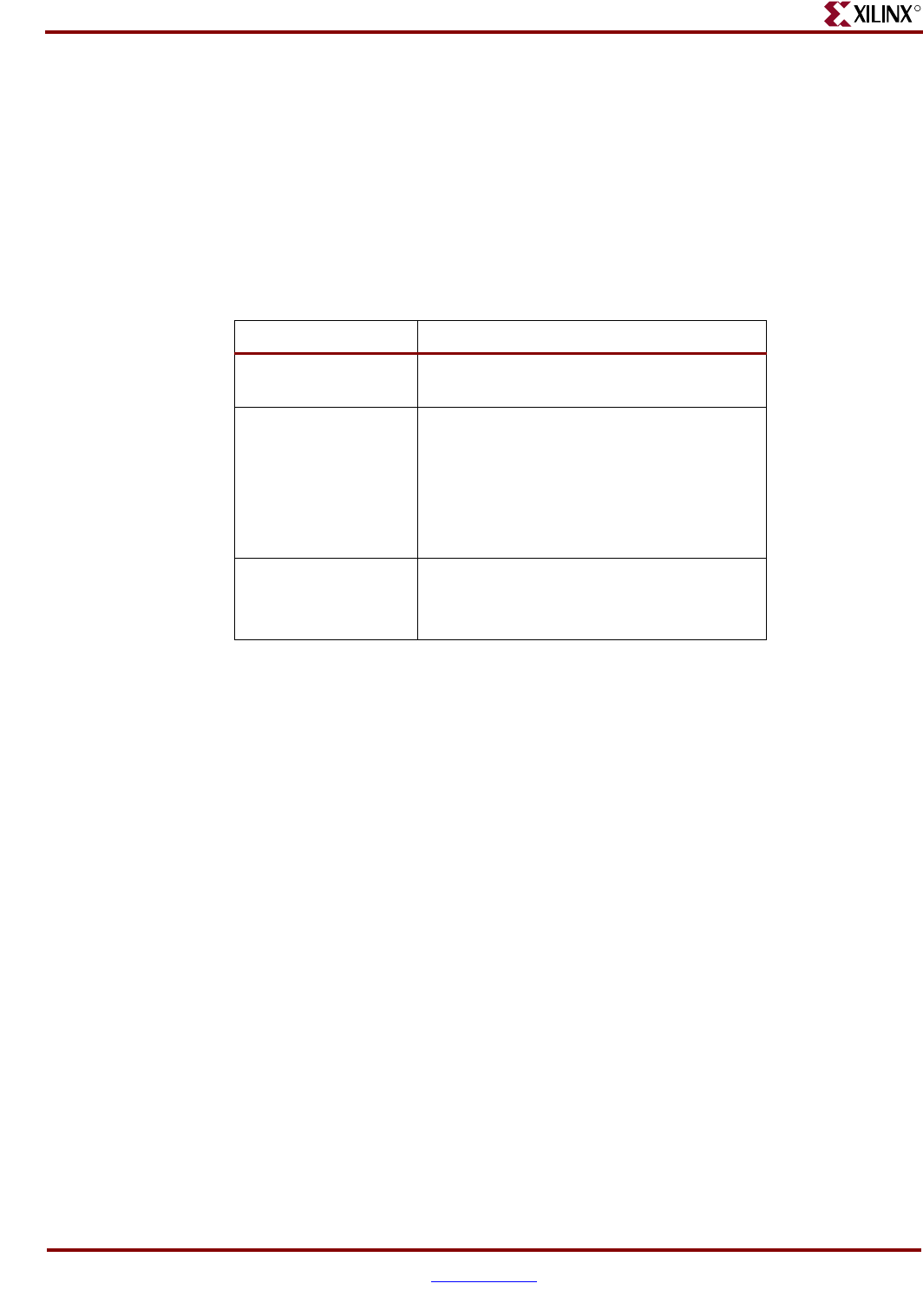

The following table lists the different design tools used for each verification type.

Table 2-1: Verification Tools

Verification Type Tools

Simulation Third-party simulators (integrated and

non-integrated)

Static Timing

Analysis

TRACE (command line program)

Timing Analyzer (GUI)

Mentor Graphics

®

TAU and Innoveda

BLAST software for use with the STAMP

file format (for I/O timing verification

only)

In-Circuit Verification Design Rule Checker (command line

program)

Download cable